Что такое микроархитектура процессора

ARM против x86: В чем разница между двумя архитектурами процессоров?

Вы наверняка знаете, что мир процессоров разбит на два лагеря. Если вы смотрите это видео со смартфона, то для вас работает процессор на архитектуре ARM, а если с ноутбука, для вас трудится чип на архитектуре x86.

А теперь еще и Apple объявила, что переводит свои Mac на собственные процессоры Apple Silicon на архитектуре ARM. Мы уже рассказывали, почему так происходит. А сегодня давайте подробно разберемся, в чем принципиальные отличия x86 и ARM. И зачем Apple в это все вписалась?

Итак, большинство мобильных устройств, iPhone и Android’ы работают на ARM’е. Qualcomm, HUAWEI Kirin, Samsung Exynos и Apple A13/A14 Bionic — это все ARM-процессоры.

А вот на компьютере не так — там доминирует x86 под крылом Intel и AMD. Именно поэтому на телефоне мы не можем запустить Word с компьютера.

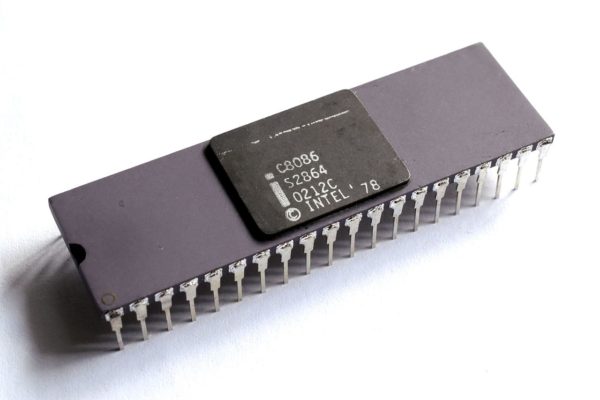

x86 — так называется по последним цифрам семейства классических процессоров Intel 70-80х годов.

Чем же они отличаются?

Есть два ключевых отличия.

Первое — это набор инструкций, то есть язык который понимает процессор

Второе отличие — это микроархитектура. Что это такое?

От того на каком языке говорят процессоры, зависит и то, как они проектируются. Потому как для выполнения каждой инструкции на процессоре нужно расположить свой логический блок. Соответственно, разные инструкции — разный дизайн процессора. А дизайн — это и есть микроархитектура.

Но как так произошло, что процессоры стали говорить на разных языках?

История CISC

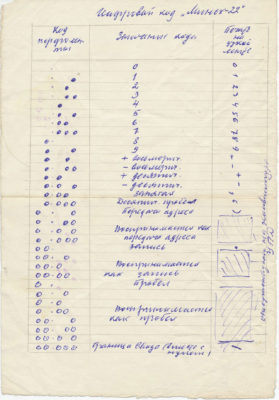

Памятка программиста, 1960-е годы. Цифровой (машинный) код «Минск-22».

Всё началось в 1960-х. Поначалу программисты работали с машинным кодом, то есть реально писали нолики и единички. Это быстро всех достало и появился Assembler. Низкоуровневый язык программирования, который позволял писать простые команды типа сложить, скопировать и прочее. Но программировать на Assembler’е тоже было несладко. Потому как приходилось буквально “за ручку” поэтапно описывать процессору каждое его действие.

Поэтому, если бы вы ужинали с процессором, и попросили передать его вам соль, это выглядело бы так:

Этот подход стал настоящим спасением как для разработчиков, так и для бизнеса. Захотел клиент новую инструкцию — не проблема, были бы деньги — мы сделаем. А деньги у клиентов были.

Недостатки CISC

Но был ли такой подход оптимальным. С точки зрения разработчиков — да. Но вот микроархитектура страдала.

Представьте, вы купили квартиру и теперь вам нужно обставить её мебелью. Площади мало, каждый квадратный метр на счету. И вот представьте, если бы CISC-процессор обставил мебелью вам гостиную, он бы с одной стороны позаботился о комфорте каждого потенциального гостя и выделил бы для него своё персональное место.

С другой стороны, он бы не щадил бюджет. Диван для одного человека, пуф для другого, кушетка для третьего, трон из Игры Престолов для вашей Дейенерис. В этом случае площадь комнаты бы очень быстро закончилась. Чтобы разместить всех вам бы пришлось увеличивать бюджет и расширять зал. Это не рационально. Но самое главное, CISC-архитектура существует очень давно и те инструкции, которые были написаны в 60-х годах сейчас уже вообще не актуальны. Поэтому часть мебели, а точнее исполнительных блоков, просто не будут использоваться. Но многие из них там остаются. Поэтому появился RISC…

Преимущества RISC

С одной стороны писать на Assembler’е под RISC процессоры не очень-то удобно. Если в лоб сравнивать код, написанный под CISC и RISC процессоры, очевидно преимущество первого.

Так выглядит код одной и той же операции для x86 и ARM.

Представьте, что вы проектируете процессор. Расположение блоков на х86 выглядело бы так.

Каждый цветной квадрат — это отдельные команды. Их много и они разные. Как вы поняли, здесь мы уже говорим про микроархитектуру, которая вытекает из набора команд. А вот ARM-процессор скорее выглядит так.

Ему не нужны блоки, созданные для функций, написанных 50 лет назад.

По сути, тут блоки только для самых востребованных команд. Зато таких блоков много. А это значит, что можно одновременно выполнять больше базовых команд. А раритетные не занимают место.

Еще один бонус сокращенного набора RISC: меньше места на чипе занимает блок по декодированию команд. Да, для этого тоже нужно место. Архитектура RISC проще и удобнее, загибайте пальцы:

Поэтому наши смартфоны, которые работают на ARM процессорах с архитектурой RISC, долго живут, не требуют активного охлаждения и такие быстрые.

Лицензирование

Но это все отличия технические. Есть отличия и организационные. Вы не задумывались почему для смартфонов так много производителей процессоров, а в мире ПК на x86 только AMD и Intel? Все просто — ARM это компания которая занимается лицензированием, а не производством.

Даже Apple приложила руку к развитию ARM. Вместе с Acorn Computers и VLSI Technology. Apple присоединился к альянсу из-за их грядущего устройства — Newton. Устройства, главной функцией которого было распознавание текста.

Даже вы можете начать производить свои процессоры, купив лицензию. А вот производить процессоры на x86 не может никто кроме синей и красной компании. А это значит что? Правильно, меньше конкуренции, медленнее развитие. Как же так произошло?

Ну окей. Допустим ARM прекрасно справляется со смартфонами и планшетами, но как насчет компьютеров и серверов, где вся поляна исторически поделена? И зачем Apple вообще ломанулась туда со своим Apple Silicon.

Что сейчас?

Допустим мы решили, что архитектура ARM более эффективная и универсальная. Что теперь? x86 похоронен?

На самом деле, в Intel и AMD не дураки сидят. И сейчас под капотом современные CISC-процессоры очень похожи на RISC. Постепенно разработчики CISC-процессоров все-таки пришли к этому и начали делать гибридные процессоры, но старый хвост так просто нельзя сбросить.

Но уже достаточно давно процессоры Intel и AMD разбивают входные инструкции на более мелкие микро инструкции (micro-ops), которые в дальнейшем — сейчас вы удивитесь — исполняются RISC ядром.

Да-да, ребята! Те самые 4-8 ядер в вашем ПК — это тоже RISC-ядра!

Надеюсь, тут вы окончательно запутались. Но суть в том, что разница между RISC и CISC-дизайнами уже сейчас минимальна.

А что остается важным — так это микроархитектура. То есть то, насколько эффективно все организовано на самом камне.

Ну вы уже наверное знаете, что Современные iPad практически не уступают 15-дюймовым MacBook Pro с процессорами Core i7 и Core i9.

А что с компьютерами?

Недавно компания Ampere представила свой 80-ядерный ARM процессор. По заявлению производителя в тестах процессор Ampere показывает результат на 4% лучше, чем самый быстрый процессор EPYC от AMD и потребляет на 14% меньше энергии.

Компания Ampere лезет в сегменты Cloud и Workstation, и показывает там отличные цифры. Самый быстрый суперкомпьютер в мире сегодня работает на ARM ISA. С обратной стороны, Intel пытается все таки влезть в сегмент low power и для этого выпускает новый интересный процессор на микроархитектуре lakefield.

И Apple та компания, которая способна мотивировать достаточное количество разработчиков пилить под свой ARM. Но суть этого перехода скорее не в противостоянии CISC и RISC. Поскольку оба подхода сближаются, акцент смещается на микроархитектуру, которую делает Apple для своих мобильных устройств. И судя по всему микроархитектура у них крута. И они хотели бы ее использовать в своих компьютерах.

И если бы Intel лицензировал x86 за деньги другим людям, то вероятно Apple просто адаптировали свою текущую микроархитектуру под x86. Но так как они не могут этого сделать, они решили просто перейти на ARM. Проблема для нас с микроархитектурой в том, что она коммерческая тайна. И мы про нее ничего не знаем.

Итоги

Спрос на ARM в итоге вырастет. Для индустрии это не просто важный шаг, а архиважный. Линус Торвальдс говорил, что пока рабочие станции не станут работать на ARM — на рынке серверов будут использовать x86.

И вот это случилось — в перспективе это миллионы долларов, вложенных в серверные решения. Что, конечно, хорошо и для потребителей. Нас ждет светлое будущее и Apple, действительно, совершила революцию!

Редактор материала: Антон Евстратенко. Этот материал помогли подготовить наши зрители Никита Куликов и Григорий Чирков. Спасибо ребята!

Микроархитектура

Содержание

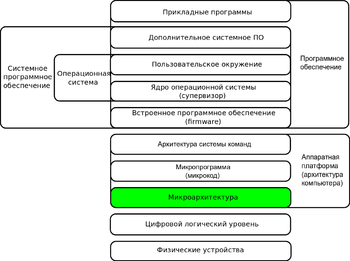

Связь с микрокодом и архитектурой набора команд

АНК — это приблизительно то же самое, что и модель программирования, с точки зрения программиста на языке ассемблера или создателя компилятора. АНК, в числе прочего, включает модель исполнения, регистры процессора, форматы адресов и данных, в то время, как микроархитектура включает составные части процессора и способы их взаимосвязи и взаимодействия для реализации АНК.

Однако во многих случаях работа элементов микроархитектуры контролируется микрокодом, встроенным в процессор. В случае наличия слоя микрокода в архитектуре процессора он выступает своеобразным интерпретатором, преобразуя команды уровня АНК в команды уровня микроархитектуры. При этом различные системы команд могут быть реализованы на базе одной микроархитектуры. [3]

Машины с различной микроархитектурой могут иметь одинаковую АНК и, таким образом, быть пригодными для выполнения тех же программ. Новые микроархитектуры и/или схемотехнические решения вместе с прогрессом в полупроводниковой промышленности являются тем, что позволяет новым поколениям процессоров достигать более высокой производительности, используя ту же АНК.

Блок-схема микроархитектуры первого в мире микропроцессора Intel 4004.

Аспекты микроархитектуры

Конвейерный тракт данных является наиболее широко используемым в современных микроархитектурах. Эта техника используется в большинстве современных микропроцессоров, микроконтроллеров и цифровых сигнальных процессоров. Конвейерная архитектура позволяет нескольким инструкциям перекрываться в исполнении, что напоминает сборочную линию. Конвейер включает несколько различных стадий, выбор которых является фундаментальным при разработке микроархитектуры. [4] Некоторые из этих стадий включают выбор инструкций, декодирование инструкций, исполнение и запись результата. Некоторые архитектуры включают другие стадии, такие как доступ к памяти. Дизайн конвейера — один из центральных вопросов проектирования микроархитектуры.

Устройства исполнения также являются ключевыми для микроархитектуры. Они включают арифметико-логические устройства, устройства обработки чисел с плавающей точкой, устройства выборки и хранения, прогнозирование ветвления, параллелизм на уровне данных (SIMD). Эти блоки производят операции или вычисления процессора. Выбор числа блоков исполнения, их задержек, пропускной способности и способа соединения памяти с системой также являются микроархитектурными решениями.

Проектные решения уровня системы, такие как включать или нет периферийные устройства типа контроллеров памяти, могут считаться частью процесса разработки микроархитектуры, поскольку они содержат решения по уровню производительности и способам соединения этих периферийных устройств.

В отличие от архитектурного дизайна, где достижение определённого уровня производительности является главной целью, проектирование микроархитектуры уделяет большее внимание другим ограничениям. Поскольку дизайн микроархитектуры прямо влияет на то, что происходит в системе, внимание должно быть уделено следующим проблемам:

Концепции микроархитектуры

В общем случае, все ЦПУ, одночиповые микропроцессоры и многочиповые реализации выполняют программы, производя следующие шаги:

Эта последовательность выглядит просто, но осложняется тем фактом, что иерархия памяти (где располагаются инструкции и данные), которая включает в себя кэш, основную память и энергонезависимые устройства хранения, такие как жёсткие диски, всегда была медленнее самого процессора. Шаг (2) часто привносит длительные (по меркам ЦПУ) задержки, пока данные поступают по компьютерной шине. Значительная часть исследований посвящена разработкам, которые позволяют избегать таких задержек, насколько это возможно. В течение многих лет главной целью было выполнять больше инструкций параллельно, увеличивая таким образом эффективную скорость выполнения программ. Эти усилия вызывают усложнение логики и структуры схем. Изначально эти техники могли быть реализованы только на дорогих мейнфреймах и суперкомпьютерах вследствие большого объёма схем, необходимого для этого. По мере того, как полупроводниковая промышленность развивалась, всё большее количество этих техник могло быть реализовано в единственном полупроводниковом чипе.

Ниже приведён краткий обзор микроархитектурных концепций, распространённых в современных процессорах

Выбор системы команд

Однако выбор системы команд в значительной степени определяет сложность реализации высокопроизводительных устройств. Известной стратегией, использовавшейся при разработке первых RISC-процессоров, было упрощение инструкций до минимума индивидуальной семантической сложности в сочетании с высокой упорядоченностью и простотой кодирования. Такие единообразные инструкции просто извлекались, декодировались и исполнялись конвейерообразным манером, позволяя реализовывать простую стратегию сокращения числа логических уровней для достижения более высоких частот функционирования. При этом кэш-память инструкций компенсировала естественно низкую плотность кода при высоких частотах работы, а большие наборы регистров использовались для исключения, насколько это возможно, обращений к (медленной) памяти.

Конвейеризация инструкций

Одна из первых и наиболее мощных техник повышения производительности — это использование конвейера инструкций. Ранние модели процессоров должны были выполнить все описанные выше шаги для одной инструкции, прежде чем перейти к следующей. Большие части схемы оставались неиспользуемыми на любом отдельном шаге. Например, часть схемы, осуществляющая декодирование инструкции, останется неиспользуемой во время её исполнения и т. д.

Конвейеры увеличивают производительность, позволяя нескольким инструкциям прокладывать свой путь через процессор в одно и то же время. В том же простом примере процессор начал бы декодировать (шаг 1) новую инструкцию, в то время как предыдущая ожидала бы результатов. В этом случае до четырёх инструкций могло находиться в обработке единовременно, позволяя процессору выглядеть в четыре раза быстрее. В то же время, любая отдельная инструкция выполняется в течение того же самого времени, поскольку существуют те же четыре шага, хотя в целом процессор выдаёт больше обработанных инструкций и может работать на значительно более высоких тактовых частотах.

RISC сделал конвейеры меньше и значительно проще в конструировании, отделив каждый этап обработки инструкций, зафиксировав длину машинной инструкции и сделав время их выполнения одинаковым — один такт или как максимум один цикл доступа к памяти (из-за выделения инструкций load и store). Процессор в целом функционирует на манер сборочной линии с инструкциями, поступающими с одной стороны и результатами, выходящими с другой. Из-за уменьшенной сложности классического RISC-конвейера, конвейерезированное ядро и кэш инструкций могли быть размещены на кристалле того же размера, который содержал бы лишь ядро в случае CISC архитектуры. Это и было истинной причиной того, что RISC был быстрее. Ранние разработки, такие как SPARC и MIPS часто работали в 10 раз быстрее CISC решений Intel и Motorola той же тактовой частоты и цены.

Конвейеры никоим образом не ограничиваются RISC разработками. В 1986 году флагманская реализация VAX (VAX 8800) была сильно конвейеризирована, несколько опережая коммерческие реализации MIPS и SPARC. Большинство современных процессоров (даже встроенных) конвейеризированы, а процессоры с микрокодом но без конвейеров можно встретить только среди наиболее ограниченных по площади встроенных решений. Большие CISC машины, от VAX 8800 до современных Pentium 4 и Athlon используют как микрокод, так и конвейеры. Улучшения в конвейеризации и кэшировании — два важнейших микроархитектурных сдвига, позволяющих производительности процессоров идти в ногу со схемными технологиями, на которых они основаны.

Когда улучшения в производстве чипов позволили размещать на кристалле ещё больше логики, начался поиск способов применения этого ресурса. Одним из направлений стало размещение прямо на кристалле чипа очень быстрой кэш памяти, доступ к которой происходил всего за несколько тактов процессора, в отличие от большого их количества при работе с основной памятью. При этом процессор также включал контроллер кэша, автоматизировавший чтение и запись данных в кэш.

RISC процессоры стали снабжаться кэшем в середине-конце 1980-х (часто объёмом всего 4 КБ). Этот объём постоянно возрастал, и современные процессоры имеют по крайней мере 512 КБ, а наиболее мощные 1,2,4,6,8 и даже 12 МБ кэш памяти, организованной в иерархию. В целом, больший объём кэша означает большую производительность вследствие меньшего времени простоя процессора.

Кэш память и конвейеры хорошо дополняют друг друга. Если первоначально не имело смысл создавать конвейеры, работающие быстрее времени доступа к основной памяти, то с появлением кэша конвейер стал ограничен лишь более короткими задержками доступа к быстрой памяти на чипе. В итоге это позволяло увеличивать тактовые частоты процессоров.

Прогнозирование ветвления

Одно из препятствий в достижении более высокой производительности за счёт параллелизма на уровне данных возникает вследствие остановки и переполнения конвейера при ветвлениях. Обычно до конца неизвестно, будет ли выбрана ветвь условного ветвления в конвейере, поскольку ветвление зависит от результата, который берётся из регистра. С того времени, как декодер инструкций процессора выяснил, что натолкнулся на инструкцию, вызывающую ветвление до того, как определяющее решение значение может быть прочитано из регистра, конвейер необходимо остановить на несколько циклов. Если ветвь выбрана, то его нужно заполнить. Одновременно с ростом частоты процессоров увеличивалась глубина конвейеров и современные разработки имеют до 20 стадий. С учётом того, что в среднем каждая пятая инструкция вызывает ветвление, без дополнительных мер возникнет значительный простой.

Такие техники, как прогнозирование ветвления и спекулятивное исполнение используются для уменьшения этих потерь. Прогнозирование ветвления заключается в том, что оборудование делает обоснованное решение о том, какая из ветвей будет выбрана для исполнения. Современные разработки имеют достаточно сложные статистические системы прогнозирования, которые используют результаты последних ветвлений для предсказания будущих с большой точностью. Такие решения позволяют аппаратуре предварительно считать инструкции, не дожидаясь результата из регистра. Спекулятивное исполнение — это дальнейшее развитие идеи, при котором инструкции из предсказанного пути не только считываются, но и исполняются до того, как становится точно известно, будет ли выбрана ветвь. Это помогает достичь высокой производительности, если решение было правильным, но вызывает риск большой потери времени, если решение ошибочно и инструкции нужно отменить.

Суперскалярность

Изначально, даже процессоры конвейерной микроархитектуры могли запускать только одну инструкцию в каждый момент времени. Очевидно, что программы могли бы выполняться быстрее, если запускать несколько инструкций одновременно. Именно этого достигают суперскалярные микроархитектуры за счёт использования нескольких одинаковых функциональных блоков, таких как АЛУ. Такие архитектуры появились когда на схеме стало возможно размещать больше элементов и к концу 1980-х они вышли на рынок.

В современных разработках часто можно видеть два устройства выборки, одно устройство хранения (многие инструкции не имеют результатов для хранения), два или более целочисленных АЛУ, два или более устройства обработки чисел с плавающей точкой, устройство SIMD и другие. Логика управления значительно усложнилась, обеспечивая чтение из памяти большого количества инструкций, распределение их по свободным функциональным блокам, сбор и упорядочение результатов.

Исполнение не по порядку

Появление кэшей сократило частоту и длительность простоев из-за ожидания чтения данных из иерархии памяти, но не устранило их совсем. В ранних разработках отсутствие данных в кэше вынуждало контроллер кэша остановить процессор и ожидать. Очевидно, что в программе почти всегда есть другие инструкции, данные для которых доступны в кэше в данный момент. Внеочередное исполнение позволяет выполнить эти инструкции в то время, как предыдущие ожидают данных из кэша. Затем результаты упорядочиваются так, что сохраняется предусмотренный в программе порядок. Эта техника также используется, чтобы избегать других остановок вследствие зависимых операндов, как в случае инструкций, ожидающих результатов длинных операций с плавающей точкой или других многоцикловых операций.

Переименование регистров

Переименование регистров — это техника, позволяющая избежать ненужного последовательного выполнения инструкций программы вследствие использования этими инструкциями одних и тех же регистров. Положим имеется две группы инструкций, использующих один регистр. Одна группа инструкций должна предшествовать другой для того, чтобы освободить этот регистр. Но если вторую группу инструкций перенаправить на другой однотипный регистр, то обе группы могут выполняться параллельно.

Многопроцессорность и многопоточность

В определённый период разработчики компьютеров оказались в тупике, связанном с растущим несоответствием между рабочими частотами ЦПУ и временем доступа к DRAM. Ни одна из технологий, эксплуатирующих параллелизм уровня инструкций внутри одной программы не могла компенсировать длительные остановки, возникающие когда данные должны быть прочитаны из основной памяти. К тому же, большое число транзисторов и высокие тактовые частоты, необходимые для более совершенных способов организации параллелизма инструкций, требовали таких уровней рассеивания тепла, что устройства нельзя было дёшево охлаждать. По этим причинам новые поколения компьютеров стали использовать более высокие уровни параллелизма, существовавшие вне одной программы или одного программного потока.

Эта тенденция также известна как производительные вычисления (throughput computing) и возникла в своё время на рынке мэйнфреймов, где OLTP требовала не столько высокой скорости обработки отдельной транзакции, сколько возможности обрабатывать большое их число одновременно. С распространением приложений, базирующихся на использовании транзакций, таких, как сетевая маршрутизация и обслуживание веб-сайтов, в компьютерной индустрии вновь появился акцент на ёмкости и пропускной способности.

Одним из способов достижения параллелизма такого вида являются многопроцессорные системы — компьютеры с несколькими ЦПУ. Когда-то ограничивавшиеся мэйнфреймами и суперкомпьютерами, многопроцессорные системы в виде миниатюрных (2-8)-процесорных серверов становятся обычным явлением в малом бизнесе. Для крупных корпораций характерны масштабные мультипроцессоры (16-256). В 1990-е появились и многопроцессорные персональные компьютеры.

По мере дальнейшего уменьшения размера транзисторов (с соответствующим увеличением их числа в интегральных микросхемах) получали распространение многоядерные процессоры, у которых несколько физических процессорных ядер размещаются в единственном кремниевом чипе. Сначала такие решения предназначались для рынка встроенных систем, где более простые и компактные архитектуры позволяли разместить несколько экземпляров ЦПУ на одном кристалле. К 2005 году полупроводниковая технология позволила поместить в один корпус два высокопроизводительных универсальных процессора. В некоторых проектах, таких, как UltraSPARC T1 Sun Microsystems, разработчики вернулись к более простым микроархитектурам (скалярным с исполнением по порядку) с тем, чтобы разместить больше процессоров на одном кристалле.

Многопоточность является ещё одной технологией, получившей распространение сравнительно недавно. Суть её в том, что когда процессору необходимо получить данные из медленной основной памяти, он вместо того, чтобы простаивать в ожидании этих данных, переключается на выполнение другого программного потока, который готов к исполнению. Не улучшая время выполнения отдельной программы, многопоточность тем не менее увеличивает пропускную способность всей системы. Концептуально операции многопоточного процессора эквивалентны переключению контекста (процесса или потока) на уровне операционной системы. Различие состоит в том, что многопоточный процессор производит переключение активного потока за один такт, в то время как программная реализация на уровне ОС требует на несколько порядков больших временных затрат. Это достигается путём аппаратной репликации регистрового контекста для каждого потока.

Дальнейшее развитие микроархитектур в этом направлении связано с одновременной многопоточностью. При этом суперскалярный процессор выполняет инструкции разных программ и потоков одновременно.