spi rom что это

Данная статья является кратким дискурсом по шине SPI и не должна восприниматься как точная техническая документация. Рассматривается только полнодуплексный вариант применения.

Общие сведения:

Несмотря на то, что интерфейс называется 4-х проводным, для подключения нескольких ведомых понадобится по одному проводу SS для каждого ведомого (в полнодуплексной реализации). Сигналы MISO, MOSI и SCK являются общими для всех устройств на шине. Ведущий посылает сигнал SS для того ведомого, обмен данными с которым будет осуществляться. Простыми словами, все ведомые, кроме выбранного ведущим будут игнорировать данные на шине. SS является инверсным (active-low), что означает что ведущему необходимо прижать эту линию для выбора ведомого.

Подключение:

SPI на Arduino:

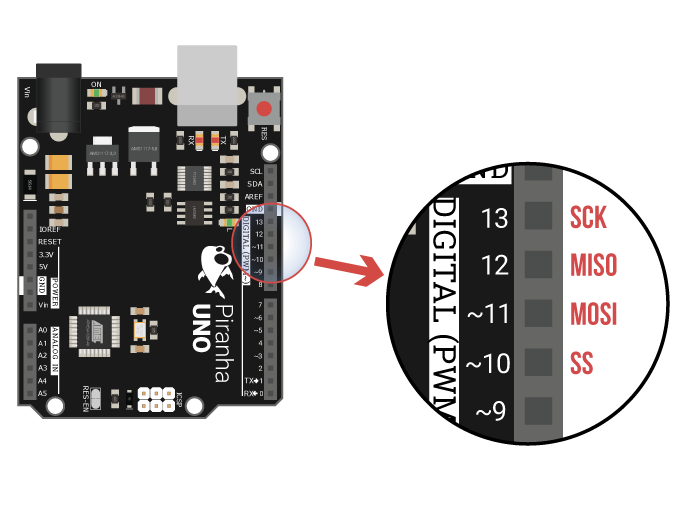

Arduino UNO/Piranha UNO/Arduino ULTRA

На Arduino UNO/Piranha UNO/Arduino ULTRA выводы аппаратного SPI расположены на 10, 11, 12 и 13 выводах, а так же эти выводы соединены с колодкой ICSP (in circuit serial programmer):

| Сигнал | Вывод |

|---|---|

| SS | 10 |

| MOSI | 11 |

| MISO | 12 |

| SCK | 13 |

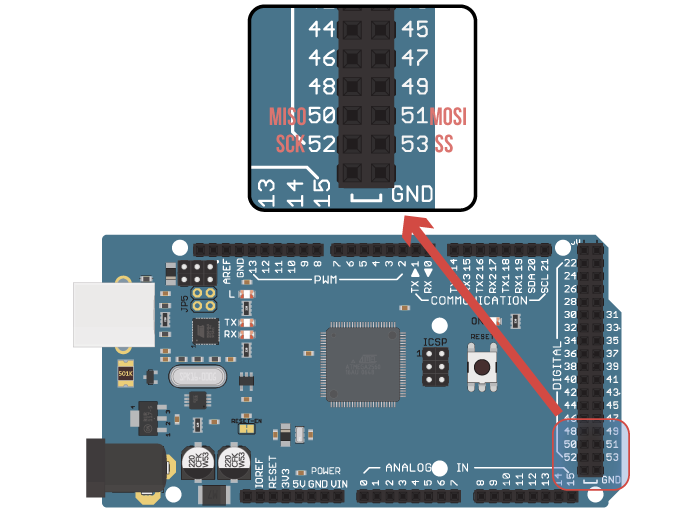

Arduino MEGA

На Arduino MEGA выводы аппаратного SPI расположены на 50, 51, 52 и 53 выводах, а так же эти выводы соединены с колодкой ICSP (in circuit serial programmer):

| Сигнал | Вывод |

|---|---|

| SS | 53 |

| MOSI | 51 |

| MISO | 50 |

| SCK | 52 |

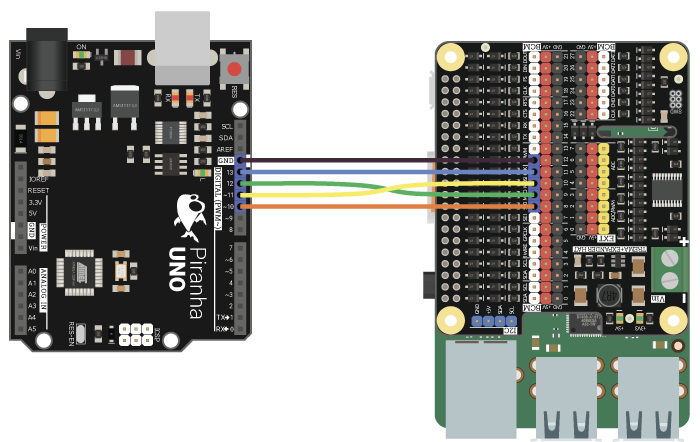

Пример для Arduino

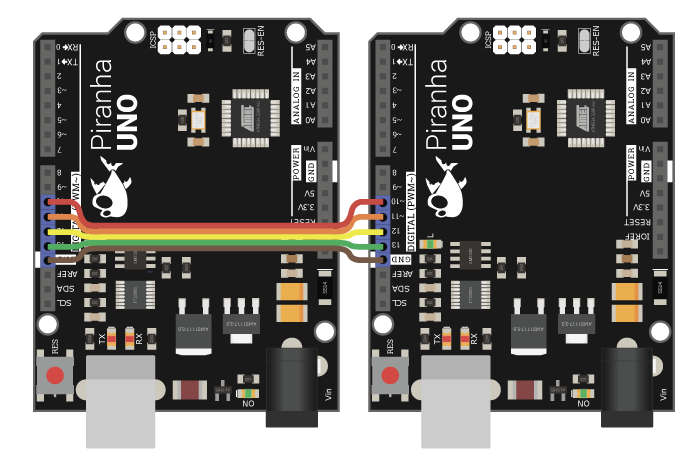

В этих примерах мы соединим две Arduino по SPI по следующей схеме:

В одну плату необходимо загрузить скетч ведущего, а в другую скетч ведомого. Для проверки работы необходимо открыть проследовательный монитор той платы, в которую загружен скетч ведомого.

Arduino UNO в качестве ведущего:

Arduino UNO в качестве ведомого:

После соединения двух Arduino по SPI и загрузки соответствующих скетчей, мы будем получать следующее сообщение в мониторе последовательного порта ведомого микроконтроллера раз в секунду:

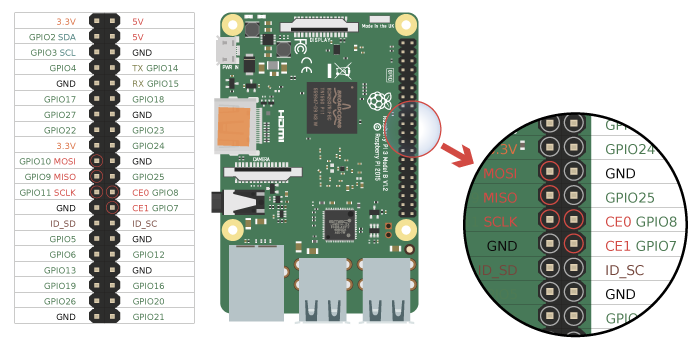

SPI на Raspberry Pi

На Raspberry Pi выводы аппаратного SPI расположены на выводах GPIO7, GPIO8, GPIO9, GPIO10, GPIO11:

Подробное описание как это сделать можно посмотреть по ссылке Raspberry Pi, включаем I2C, SPI

Пример работы с SPI на Python:

В отличие от Arduino для Raspberry не существует простых решений для работы в режиме ведомого. Подробней ознакомиться с работой чипа BCM Raspberry можно в технической документации на официальном сайте, стр. 160.

Для проверки работы сценария можно подключить Raspberry по SPI к Arduino со скетчем из примера выше через преобразователь уровней или Trema+Expander Hat:

Подробнее о SPI

Параметры

Существуют четыре режима работы SPI, зависящие от полярности (CPOL) и фазы (CPHA) тактирования:

| Режим | Полярность | Фаза | Фронт тактирования | Фронт установки бита данных |

|---|---|---|---|---|

| SPI_MODE0 | 0 | 0 | Спадающий | Нарастающий |

| SPI_MODE1 | 0 | 1 | Нарастающий | Спадающий |

| SPI_MODE2 | 1 | 0 | Нарастающий | Спадающий |

| SPI_MODE3 | 1 | 1 | Спадающий | Нарастающий |

В Arduino IDE для установки режима необходимо передать функции, возвращающей объект настроек параметр режима работы SPI_MODE, например:

Для выбора режима работы SPI на Raspberry Pi необходимо вызвать дескриптор объекта SpiDev().mode и присвоить ему битовые значения CPOL и CPHA, например:

Скорость передачи данных

Скорость передачи данных устанавливается ведущим и может меняться «на лету». Программист в силах указать лишь максимальную скорость передачи данных.

BIOS ROM c интерфейсом SPI.

BIOS ROM c интерфейсом SPI

Когда в качестве носителя BIOS начали использовать микросхемы Flash ROM, допускающие перезапись содержимого без физического вмешательства в компьютер, то появилась возможность оперативной перезаписи (обновления) BIOS, и это привело к риску его случайного или преднамеренного искажения. Поэтому появились и новые методы защиты BIOS от несанкционированного искажения. Появились и новые типы микросхем Flash ROM и интерфейсы для их подключения.

Рис. 1. ICH10 и ПЗУ BIOS

Интерфейс SPI. Основная архитектура шины SPI для базового варианта интерфейса приведена на рис. 2 (классическая четырех проводная структура). В ней один ведущий управляет несколькими (N) ведомыми. Все ведомые подключены параллельно на линиях SCLK, MISO и MOSI шины SPI. Выборка ведомого происходит с помощью одной из линий портов ввода/вывода, которая соединяется с входом NSS соответствующего ведомого. Обычно такая архитектура используется для построения систем с одним микроконтроллером, исполняющим роль ведущего, и рядом периферийных микросхем, исполняющих роль ведомых. В качестве периферийных микросхем может быть использован ряд современных микросхем, оснащенных интерфейсом SPI, например, таймеры реального времени RTC, аналого-цифровые преобразователи ADC, цифро-аналоговые преобразователи DAC, различные микросхемы памяти Flash-ПЗУ и т. п.

Рис. 2. Основная архитектура шины SPI (базовый вариант)

Частным случаем предыдущей архитектуры является трех проводная структура, приведенная на рис. 3. в ней ведомая микросхема постоянно выбрана, и необходимость в использовании четвертой линии интерфейса SPI отсутствует.

Рис. 3. Трехпроводная структура шины SPI

При обмене данными по интерфейсу SPI контроллер может работать как в режиме Master, так и в режиме Slave. При этом пользователь может задать следующие параметры:

— скорость передачи (четыре программируемых значения);

— формат передачи (от младшего разряда к старшему или наоборот).

Дополнительной возможностью подсистемы SPI является «пробуждение» микроконтроллера из режима Idle при поступлении данных. Модуль SPI использует четыре внешних вывода микроконтроллера. Как и для большинства периферийных устройств микроконтроллера, эти выводы являются линиями порта ввода/вывода общего назначения. В ряде случаев пользователь должен самостоятельно задать режим работы вывода, используемого модулем SPI, в соответствии с его назначением, причем возможность управления внутренними подтягивающими резисторами выводов, работающих как входы, сохраняется независимо от способа управления их режимом работы.

Обмен данными осуществляется (передаваемые данные записываются, а принимаемые данные считываются) через регистр данных (SPDR). Запись в этот регистр инициирует начало передачи, а при его чтении считывается содержимое приемного буфера сдвигового регистра. Поэтому этот регистр можно назвать буфером между регистровым файлом микроконтроллера и сдвиговым регистром модуля SPI. Перед началом выполнения обмена необходимо разрешить работу модуля SPI. При подключении к ведущему устройству нескольких ведомых, что разрешено спецификацией SPI, выбор конкретного ведомого устройства осуществляется подачей на его вход SS сигнала «низкого уровня».

Производители микросхем в своей документации могут использовать и другие обозначения этих сигналов, например:

Рис. 4. Режим обмена SPI Mode 0

Рис. 5. Режим обмена SPI Mode 1

Рис. 6. Режим обмена SPI Mode 2

Рис. 7. Режим обмена SPI Mode 3

Микросхемы SPI-Flash (в том числе и SST25VF080B), используют только 3 сигнала для приема/передачи данных: SCK (Serial Clock) – вход тактовой частоты; SI (Serial Input) – вход данных (побитно адрес/данные/коды команд); SO (Serial Output) – выход данных (побитно данные/состояние микросхемы). Для защиты от записи используется cигнал WP#, защита от записи программного обеспечения осуществляется через биты защиты блока в регистре статуса, сигнал HOLD# приостанавливает последовательность обращения к памяти (не отбрасывая устройство), используется гибкая система стирания (однородными 4-килобайтными секторами, 32- килобайтными оверлейными блоками, однородными 64- килобайтными оверлейными блоками – см. табл. 2).

Процессор после окончания «своего» сигнала «начального сброса» должен приступить к выборке первой исполняемой команды из ПЗУ BIOS, что должно подтверждаться присутствием цикла обращения к этой микросхеме через интерфейс SPI (Serial Peripheral Interface). Платформа, использующая интерфейс SPI, также поддерживает чтение содержимого микросхемы ПЗУ BIOS, но для передачи управляющей и статусной информации во время записи и стирания Flash ROM, используется другой метод доступа. Информация для выполнения цикла на шине SPI (адрес и данные) записывается в специальные регистры контроллера SPI (Flash Address и Flash Data соответственно), затем в регистр Software Sequencing Flash Control передается команда на выполнение цикла обращения к Flash ROM (чтения или записи). Микросхемы SPI-Flash (рис. 8), используют 3 сигнала для приема/передачи данных: SCK (Serial Clock) – вход тактовой частоты; SI (Serial Input) – вход данных (побитно адрес/данные/коды команд; SO (Serial Output) – выход данных (побитно данные/состояние микросхемы). Обращение к ПЗУ BIOS начинается с выдачи активного низкого уровня сигнала на вход CE# (см. рис. 9). Описание контактов микросхемы SST 25VF080B приведено в табл. 1.

На рис. 9, 10, 11, 12 приведены примеры протоколов операций на интерфейсе SPI.

Таблица 2. Программирование Status Register Block Protection для SST25VF080B

Таблица 3. Device Operation Instructions (команды операций устройства)

Рис. 10. Операция стирания блоком 32-KByte и 64-KByte на SPI (код операции 52H и D8H)

Рис.11. Операция «Чтение» Read-Status-Register (RDSR), код операции 05H

Рис. 12. Write-Enable (WREN), Write Disable (WRDI), код операции 06H и 04H

Для перезаписи содержимого микросхемы BIOS, программа должна взаимодействовать с двумя блоками регистров:

— регистры интерфейса Flash ROM, расположенные в составе «южного моста» чипсета,

— и регистры, входящие в состав самой микросхемы Flash ROM.

При переходе от интерфейса LPC к SPI, архитектура двух указанных блоков существенно изменилась (контроллер SPI, входящий, например, в состав «южного моста» Intel ICH8, содержит более 20 регистров управления и состояния). Регистры адресуются в пространстве памяти с использованием технологии memory-mapped I/O (описание всех регистров и команд контроллера SPI выходит за рамки данной статьи, мы ограничимся регистрами, используемыми при выполнении основных операций – чтении идентификаторов, записи и стирании Flash ROM).

Физический доступ к микросхеме BIOS (не надо путать с областью Shadow RAM) осуществляется посредством окна, примыкающего к верхней границе диапазона 0-4GB. Например, Flash ROM размером 1 Мбайт будет доступен в диапазоне FFF00000h-FFFFFFFFh. В платформах, использующих интерфейс LPC, через тот же диапазон, при выполнении операций стирания и записи выполняется передача команд и записываемых данных для микросхемы Flash ROM, а также чтение ее статуса.

Платформа, использующая интерфейс SPI, рассматриваемая в данной статье, также поддерживает чтение содержимого микросхемы BIOS через указанный диапазон, но для передачи управляющей и статусной информации во время записи и стирания Flash ROM, используется другой метод доступа. Информация для выполнения цикла на шине SPI (адрес и данные) записывается в специальные регистры контроллера SPI (Flash Address и Flash Data соответственно), затем в регистр Software Sequencing Flash Control передается команда на выполнение цикла обращения к Flash ROM (чтения или записи). После этого, через регистр Software Sequencing Flash Status можно определить момент завершения операции и проконтролировать наличие ошибок. Данные, прочитанные из Flash ROM, находятся в регистре Flash Data.

В платформах с интерфейсом LPC, передача команд выполнялась путем прямой записи байта кода команды в адресный диапазон Flash ROM. Интерфейс SPI использует косвенный метод передачи команд посредством 8-байтного регистра OpCode Menu. Каждый из байтов этого регистра хранит код одной из команд для управления Flash ROM (запись, стирание, чтение идентификатора и т.п.). Для запуска требуемой операции, программа должна передать номер байта (от 0 до 7), который содержит код этой операции. Этот номер передается в 3-битном поле COP (Cycle Opcode Pointer), которое является частью 32-битного кода, записываемого в регистр Software Sequencing Flash Control для запуска команды на выполнение. Блок регистров OpCode Menu обычно инициализирует BIOS при старте платформы. Расположение байтов кодов операций в 8-байтном блоке зависит от реализации BIOS и может быть произвольным, поэтому программа должна просканировать данный блок и определить, под каким номером расположена в нем требуемая команда. Этот номер и будет использован при заполнении поля COP. Варианты заполнения могут быть разными, даже среди материнских плат одной модели, использующих различные версии BIOS. Некоторые утилиты перезаписи Flash изменяют содержимое указанных регистров.

Механизмы доступа к Flash ROM и защита записи. В общем случае, для инициирования операций стирания или перезаписи микросхемы BIOS, программа должна выполнить четыре действия:

— настроить регистры «южного моста» чипсета, управляющие размещением микросхемы BIOS в адресном пространстве для обеспечения доступа к полному объему микросхемы;

— выключить режим защиты записи BIOS, реализуемый средствами «южного моста» чипсета;

— выключить режим защиты записи BIOS, реализуемый средствами микросхемы Flash ROM;

— передать команду стирания или записи микросхеме Flash ROM.

Рассмотрим подробнее эти процедуры, механизмы защиты, препятствующие их несанкционированному выполнению и, конечно, точки уязвимости этих механизмов. Как было сказано выше, при выполнении операций записи и стирания, программный доступ к микросхеме SPI Flash осуществляется посредством регистров контроллера SPI, без использования диапазона адресов, в котором доступен образ микросхемы BIOS. Поэтому перенастройка чипсета для доступа к диапазону FFF00000h-FFFFFFFFh в данном примере не потребуется. Защита записи, реализуемая «южным мостом» Intel ICH8 построена по такой же схеме, как и в платформах предыдущих поколений, отличаются только адреса регистров.

Доступом к микросхеме BIOS управляет 8-битный регистр BIOS_CNTL (его координаты в конфигурационном пространстве Bus=0, Device=1Fh, Function=0, Register=DCh).

Бит 0 этого регистра (бит BIOSWE, BIOS Write Enable) управляет разрешением записи в микросхему BIOS, 0=запрещена, 1=разрешена. Бит 1 того же регистра (бит BLE, BIOS Lock Enable) обеспечивает перехват несанкционированного выключения защиты. Если бит BLE=1, то при попытке установить бит BIOSWE=1 будет генерироваться прерывание SMI (System Management Interrupt) с вызовом специальной процедуры, входящей в состав BIOS. Причем, если BIOS при старте установит бит BLE=1, программно обнулить его чипсет не позволяет, режим перехвата будет выключен только после аппаратного сброса (по сигналу RESET). Данный механизм «защиты от снятия защиты» обычно не активируется разработчиками BIOS. Во всех материнских платах, исследованных автором, бит BLE=0, поэтому для снятия защиты записи достаточно установить бит BIOSWE=1, эта операция не будет перехвачена.

Микросхема Intel ICH8 также поддерживает защиту содержимого микросхемы BIOS, путем задания адресных диапазонов, защищенных от чтения и (или) записи.Теоретически, на базе данного механизма можно реализовать эффективную защиту, так как запрет программно включается процедурами BIOS при старте платформы, и может быть снят только при аппаратном сбросе. Но и этот механизм обычно не активируется разработчиками BIOS.

Обзор шины SPI и разработка драйвера ведомого SPI устройства для embedded Linux (Часть первая, обзорная)

В этой статье я хочу провести краткий обзор шины SPI (интерфейса, широко распространённого во встраиваемой технике, используемого для подключения различных устройств) и попытаюсь описать процесс создания драйвера протокольного уровня SPI устройства для Linux. Данный документ не претендует на роль полного руководства, а скорее преследует цель указать нужное направление. Так как статья не вошла в размер одного топика, мне пришлось разбить её на две части.

0. Вместо введения

Что это за статья?

Эта статья представляет собой компиляцию информации из различных источников, вольный перевод некоторых частей документации, а также мои собственные комментарии, дополнения и описания возникших проблем.

Первый подраздел описывает работу шины SPI, данная часть статьи конкретно к Linux никак не привязана, поэтому её можно читать тем, кому Linux не интересен, а нужно лишь получить информацию об этом интерфейсе.

Второй подраздел описывает структуры и механизмы лежащие в основе работы с SPI в Linux, его нужно прочесть для понимания того, о чём пойдёт речь в третьей и четвёртой частях.

Если вас не интересует мои переводы и дополнения, можете смело переходить сразу к пятой части, там можно найти информацию о том, где получить всю необходимую информацию по данному вопросу.

Если вы видите ссылки в названии какой-либо структуры или функции, можете открыть её в новой вкладке, так вы сможете попасть непосредственно на описание данной структуры/функции в официальной документации к ядру Linux.

Ошибки

Я не волшебник, я только учусь. Если найдёте какие-либо ошибки или неточности, пожалуйста, сообщите мне.

1. Что такое SPI?

Аббревиатура SPI означает «Serial Peripheral Interface» или в русском варианте «последовательный периферийный интерфейс». Название говорит само за себя, данный интерфейс используется для работы с различными периферийными устройствами. Например, это могут быть различные ЦАП/АЦП, потенциометры, датчики, расширители портов ввода/вывода (GPIO), различная память и даже более сложная периферия, такая как звуковые кодеки и контроллеры Ethernet.

С технической точки зрения SPI — это синхронная четырёхпроводная шина. Она представляет собой соединение двух синхронных сдвиговых регистров, которые является центральным элементом любого SPI устройства. Для соединения используется конфигурацию ведущий/ведомый. Только ведущий может генерировать импульсы синхронизации. В схеме всегда только один ведущий (в отличие от той же шины I2C, где возможен вариант с более чем одним ведущим), количество ведомых может быть различно. В общем случае выход ведущего соединяется со входом ведомого, и наоборот, выход ведомого соединяется со входом ведущего. При подаче импульсов синхронизации на выход SCK, данные выталкиваются ведущим с выхода MOSI, и захватываются ведомым по входу MISO. Таким образом если подать количество импульсов синхронизации соответствующее разрядности сдвигового регистра, то данные в регистрах обменяются местами. Отсюда следует что SPI всегда работает в полнодуплексном режиме. А вот нужны ли нам данные, полученные от устройства при записи какого-либо параметра, это уже другой вопрос. Часто бывает что данные полученные от устройства при записи в него данных являются мусором, в таком случае их просто игнорируют, но мы их получим вне зависимости от нашего желания.

Контроллер SPI, как правило, реализуется периферийным блоком в MCU или eMPU. В большинстве чипов он может работать как в режиме ведущего, так и в режиме ведомого. Но на данный момент Linux поддерживает только режим ведущего (Master).

Существует несколько способов включения SPI устройств.

Простейший из них вы видите на рисунке выше (спасибо Wikipedia за рисунки под свободной лицензией GFDL). В данном случае к ведущему все ведомые подключаются параллельно, за исключением сигнала выбора ведомого (

CS). Для каждого ведомого необходим отдельный сигнал выбора ведомого (на рисунке они обозначены как SSx). Для сигналов выбора ведомого могут использоваться как специально предназначенные для этого выходы SPI-контроллера, так и порты ввода/вывода общего назначения (GPIO) микроконтроллера.

CS — Chip Select (выбор микросхемы). С помощью данного сигнала происходит активация ведомого устройства. Обычно он является инверсным, то есть низкий уровень считается активным. Иногда его называют

SS (Slave Select, рус. «выбор ведомого»).

Частным случаем независимого подключения является вариант с одним единственным ведомым. В таком случае может возникнуть желание подтянуть сигнал

CS к земле, чтобы устройство всегда было в активном состоянии. Но делать это крайне не рекомендуется, так как ведомое устройство может использовать сигнал CS для инициализации или для других служебных целей.

Основное неудобство при независимом подключении ведомых в том, что для каждого из ведомых необходим отдельный сигнал

CS. Каскадная схема подключения, в зарубежной литературе называемая «daisy-chain» (можно перевести как «гирлянда»), лишена такого недостатка.

Как видно из рисунка выше, здесь используется общий сигнал выбора ведомого для всех ведомых. Выход каждого из ведомых соединяется со входом следующего. Выход последнего ведомого соединяется со входом ведущего, таким образом образуется замкнутая цепь. При таком подключении можно считать что последовательно соединённые устройства образуют один большой сдвиговый регистр. Соответственно, данные можно записать во все устройства «за один присест», предварительно собрав нужный пакет, объединяющий данные для каждого из устройств в порядке соответствующем физическому порядку соединения. Но тут есть один тонкий момент. Во-первых, все микросхемы должны поддерживать такой тип подключения; во-вторых, ядро Linux не поддерживает такой тип подключения, так что если всё же захотите его использовать, то вам придётся модифицировать существующие драйвера, либо же написать собственные.

CS и MISO не показаны. Но в данном случае они не так интересны, например, сигнал

CS представляет собой просто «провал» на всём протяжении передачи данных.

2. Обзор SPI подсистемы в Linux

Драйверы SPI в Linux делятся на две части. Первая — это драйверы SPI контроллеров, которые работают непосредственно с железом конкретно взятого контроллера. Такие драйверы определяют как настроить контроллер, какие действия предпринять при переходе в режим пониженного энергопотребления (suspend) и выходе из него(resume), выбор следующей передачи (spi_transfer) из очереди передач в сообщении (spi_message, об очередях чуть ниже) и отправка его непосредственно в порт, также определяется как активировать/деактивировать конкретное устройство посредством CS (функции cs_activate/cs_deactivate). В этой статье я не буду описывать данный тип драйверов. Как правило, они уже реализованы для тех MCU/eMPU на которые существует порт Linux, и лезть в них руками надо только в том случае, если вам нужна какая-то специфичная функция, вроде Chip Select Decoding, для возможности активации нужного ведомого устройства посредством внешней логики. Иногда это бывает полезно, например, в случае недостатка GPIO.

Вторая часть — это протокольные драйверы, используемые для работы с различными ведомыми устройствами, которые подключены к шине SPI. Данные драйверы называют «протокольными», потому что они лишь отправляют и получают различные данные от ведомых устройств, при этом не работая напрямую с каким-либо оборудованием. Именно данный тип драйверов нам наиболее интересен, так как позволяет добавить поддержку интересующего ведомого устройства в систему, его то мы и рассмотрим.

Большинство протокольных драйверов представляет собой модули ядра. Например, если устройство представляет собой аудиокодек подключаемый по SPI, то драйвер будет также использовать функции предоставляемые ALSA, а программы (например, madplay) смогут работать с ним посредством символьного устройства /dev/audio, не имея ни малейшего понятия о том как он аппаратно устроен и к какой шине подключен.

Также ядро предоставляет протокольный драйвер общего назначения, называемый spidev, с интерфейсом в виде символьного устройства. Он позволяет совершать полудуплексные обращения к ведомому SPI-устройству посредством стандартных системных вызовов read() и write(), устанавливать режим работы, а также производить полнодуплексный обмен данными посредством ioctl() вызовов.

transfers — связанный список передаваемых сегментов в транзакции (передач);

spi — указатель на spi устройство, в очереди которого стоит данное сообщение;

is_dma_maped — если данный флаг «истина», то предоставлены оба, dma и cpu виртуальные адреса для каждого буфера передачи;

complete — обратный вызов, вызываемый для извещения об окончании транзакции;

context — аргумент для обратного вызова complete();

actual_length — полное число байт, которые были переданы во всех успешных предачах;

status — 0 в случае успеха, либо отрицательное значение с errno в случае ошибки;

Структура spi_message используется для выполнения атомарной последовательности передач данных, каждая из которых представлена структурой spi_transfer. Последовательность передач «атомарна» в том смысле, что шина SPI не может быть использована для передачи другого сообщения spi_message до тех пор, пока не будет полностью отправлено предыдущее. На некоторых системах, многие такие последовательности могут быть выполнены как единая запрограммированная DMA передача. На всех системах данные сообщения ставятся в очередь, и могут быть завершены уже после транзакций с другими устройствами. Все обращения к отдельно взятому ведомому устройству всегда выполняются в FIFO порядке.

Структура struct spi_transfer описывает отдельную передачу в связанном списке сообщения и определяет пару буферов для чтения/записи.

tx_buf — указатель на буфер данных в пространстве памяти ядра, которые необходимо передать, либо NULL;

rx_buf — указатель на буфер данных в пространстве памяти ядра, в который данные следует считать, либо NULL;

len — размер буферов rx и tx в байтах;

tx_dma — DMA адрес tx_buf, используется если установлен параметр spi_message.is_dma_mapped;

rx_dma — DMA адрес rx_buf, используется если установлен параметр spi_message.is_dma_mapped;

speed_hz — устанавливает скорость для передачи, отличную от установленной по-умолчанию для устройства. Если данное значение равно 0, то используется скорость по-умолчанию, указанная в поле max_speed_hz структуры spi_device.

bits_per_word — устанавливает количество бит на слово, отличное от определённого по умолчанию. Если данное значение равно 0, то используется значенние по-умолчанию, указанное в поле bits_per_word структуры spi_device.

delay_usecs — время ожидания в микросекундах, после того как был отправлен последний бит передачи и перед тем как сменить состояние chipselect’а, либо начать передачу следующей передачи в очереди. Будьте крайне осторожны с данным параметром, нужно смотреть в какой части драйвера контроллера реализуется задержка. Например, для чипов серии at91 она реализована в обработчике прерывания, так что её использование чревато последствиями.

При инициализации структуры spi_transfer существует очень важный момент, они обязательно должны быть выделены в области памяти доступной для DMA через kmalloc, kzalloc и иже с ними. Если master-драйер использует dma, то при использовании статически объявленных массивов драйвер будет падать при попытке передачи.

При передаче данных по SPI количество записанных бит всегда равно количеству считанных. Протокольные драйверы всегда должны предоставлять указатели на буферы tx_buf и/или rx_buf. В некоторых случаях они могут предоставлять DMA адреса для передаваемых данных.

Возможность переопределения скорости передачи данных и количества бит на слово для каждой передачи в отдельности зависит от конкретной реализации драйвера и аппаратных возможностей контроллера. Например, для контроллера SPI в чипах серии at91 возможность переопределения полей speed_hz и bits_per_word не предусмотрена, поэтому они должны быть всегда установлены в 0, иначе вы получите ошибку при попытке передачи данных.

Если указатель на tx_buf установлен как NULL, то SPI контроллер будет выталкивать нули при заполнении буфера rx_buf. В случае, когда rx_buf установлен в NULL, считываемые данные будут игнорироваться. Количество выталкиваемых (и захватываемых) байтов всегда равно len. Попытка вытолкнуть только часть слова приведёт к ошибке. (Например, при попытке выталкивании трёх байт и длине слова 16 бит или 20 бит, в первом случае будет использовано 2 байта на слово, во втором — 4 байта).

Данные для передачи всегда хранятся в порядке специфичном для данной аппаратной платформы. При отправке/считывании данных происходит автоматическое конвертирование порядка байт из специфичного для SPI (обычно big-endian, за исключением случая когда выставлен параметр SPI_LSB_FIRST) в аппаратно-специфичный порядок для данного CPU. Например, если параметр bits_per_word равен 16, то буферы будут занимать по 2N байт, и содержать по N слов с длиной 16 бит каждое, хранящемся в байтовом порядке, специфичным для данного CPU.

В том случае, если размер слова не является степенью двойки, то представление слова в памяти включает дополнительные биты. Слова, хранящиеся в памяти для протокольного драйвера всегда являются выровненными по правому краю (right-justified), так что дополнительные биты всегда будут являться старшими разрядами.

Для наглядности снова приведу осциллограмму:

В данном случае tx-буфер содержит значение 0xf98e, установленное значение bits_per_word соответствует 12 битам на слово. Устройство работает в SPI_MODE_0. На рисунке синяя линия соответствует выходу MOSI контроллера, а жёлтая — SCK. Здесь хорошо видно что при отправке пришло только 0x098e, старшие четыре бита были отброшены, так как они считаются дополнительными. Если совсем просто, то одно 12-битное слово занимает в памяти два байта, а разница между размером слова в памяти и его действительным размером составляет 2*8 — 12 = 4 бита, которые отбрасываются при передаче.

SPI не поддерживает какого-либо механизма автоматического обнаружения устройств. К тому же, в большинстве случаев, SPI устройства не предусматривают горячее подключение/отключение, поэтому они, как правило, просто распаиваются непосредственно на плате. В связи с этим данные устройства считаются специфичными для конкретной платы (board-specific). Параметры для таких устройств указываются в файле платы: arch/. /mach-*/board-*.c.

Например, вот так будет выглядеть установка параметров для аудиокодека tlv320aic23b для отладочной платы SK-AT91SAM9260:

где modalias – название драйвера ядра, отвечающего за обслуживание устройства (в нашем случае “tlv320aic23b”);

chip_select – номер соответсвующего chip select’а;

max_speed_hz – максимальная частота в Гц;

mode – режим SPI, определяемый константами SPI_MODE_0… SPI_MODE_3, также через операцию битового “или” могут быть добавлены флаги SPI_CS_HIGH (устанавливает активным высокий уровень для chipselect-а ), SPI_NO_CS (передача данных без активации CS в принципе). Полный список возможных флагов можно посмотреть в описании структуры spi_device;

bus_num – номер шины (как правило, соответсвует номеру SPI контроллера в даташите на MCU/eMPU).

Также структура spi_board_info содержит следующие поля, не инициализированные в примере выше:

const void *platform_data – данное поле предназначено для хранения указателя на данные специфичные для конкретного драйвера;

void *controller_data – для некоторых контроллеров необходима информация о настройке устройства, например, DMA;

int irq – зависит от подключения устройства.

Все поля структуры spi_board_info устанавливают соответствующие поля структуры spi_device.

В случае необходимости установки параметров для других SPI устройств, в масив добавляются ещё аналогичые элементы.

Данные структуры хранят информацию, которая не может быть всегда определена драйверами. Информация, которая может быть определена функцией probe() драйвера (например, количество бит на слово), в данную структуру не включается.

Стоит заметить, что всё же существует возможность горячего подключения ведомых SPI устройств. В этом случае используют функцию spi_busnum_to_master() для получения указателя на структуру spi_master по номеру шины SPI и дальнейшего перебора устройств на шине. Но данная тема выходит за рамки данной статьи.