tpu процессор что это

Бенчмарк нового тензорного процессора Google для глубинного обучения

Каждое устройство Cloud TPU состоит из четырёх «чипов TPUv2». В чипе 16 ГБ памяти и два ядра, каждое ядро с двумя юнитами для умножения матриц. Вместе два ядра выдают 45 TFLOPS, в общей сложности 180 TFLOPS и 64 ГБ памяти на один TPU

Большинство из нас осуществляет глубинное обучение на Nvidia GPU. В настоящее время практически нет альтернатив. Тензорный процессор Google (Tensor Processing Unit, TPU) — специально разработанный чип для глубинного обучения, который должен изменить ситуацию.

Через девять месяцев после первоначального анонса две недели назад Google наконец-то выпустила TPUv2 и открыла доступ первым бета-тестерам на платформе Google Cloud. Мы в компании RiseML воспользовались возможностью и прогнали парочку быстрых бенчмарков. Хотим поделиться своим опытом и предварительными результатами.

Давно мы ждали появления конкуренция на рынке оборудования для глубинного обучения. Она должна разрушить монополию Nvidia и определить, как будет выглядеть будущая инфраструктура глубинного обучения.

Имейте в виду, что TPU пока в ранней бета-версии, о чём явно и повсеместно напоминает Google — так что некоторые обсуждаемые оценки могут измениться в будущем.

TPU в облаке Google

В то время как первое поколение чипов TPUv1 ориентировалось на ускорение вывода данных, нынешнее второе поколение в первую очередь фокусируется на ускорении обучения. В основе TPUv2 — систолический массив, отвечающий за умножение матриц, которые активно используются в глубинном обучении. Согласно слайдам Джеффа Дина, каждое устройство Cloud TPU состоит из четырёх «чипов TPUv2». В чипе 16 ГБ памяти и два ядра, каждое ядро с двумя юнитами для умножения матриц. Вместе два ядра выдают 45 TFLOPS, в общей сложности 180 TFLOPS и 64 ГБ памяти на один TPU. Для сравнения, у нынешнего поколения Nvidia V100 всего 125 TFLOPS и 16 ГБ памяти.

Чтобы использовать тензорные процессоры на платформе Google Cloud, нужно запустить Cloud TPU (предварительно получив на него квоту). Нет необходимости (и возможности) назначить Cloud TPU конкретному инстансу виртуальной машины. Вместо этого доступ TPU из инстанса осуществляется по сети. Каждому Cloud TPU присваивается имя и IP-адрес, которые следует указать в коде TensorFlow.

Создание нового Cloud TPU. Обратите внимание, что у него есть IP-адрес. Анимация GIF

TPU поддерживаются только в TensorFlow версии 1.6, которая пока в статусе релиз-кандидата. Кроме того, для VM не нужны никакие драйверы, поскольку весь необходимый код включён в состав TensorFlow. Код для выполнения на TPU оптимизируется и компилируется JIT-компилятором XLA, тоже входящим в состав TensorFlow.

Чтобы эффективно использовать TPU, код должен быть основан на высокоуровневых абстракциях класса Estimator. Затем переходим к классу TPUEstimator, который выполняет множество необходимых задач для эффективного использования TPU. Например, настраивает очереди данных для TPU и распараллеливает вычисления между ядрами. Определённо есть способ обойтись без использования TPUEstimator, но нам пока не известны такие примеры или документация.

Когда всё настроено, запускайте свой код TensorFlow как обычно. TPU обнаружатся при загрузке, график расчётов скомпилируется и будет передан туда. Интересно, что TPU ещё умеет напрямую читать и записывать в облачное хранилище контрольные точки и сводки (event summaries). Для этого нужно разрешить запись в облачное хранилище в аккаунте Cloud TPU.

Бенчмарки

Конечно, самое интересное — реальная производительность тензорных процессоров. В репозитории TensorFlow на GitHub есть набор проверенных и оптимизированных моделей TPU. Ниже показаны результаты экспериментов с ResNet и Inception. Ещё мы хотели посмотреть, как обсчитывается модель, не оптимизированная для TPU, поэтому адаптировали модель для классификации текста на архитектуре долгой краткосрочной памяти (LSTM) для запуска на TPU. Вообще-то Google рекомендует использовать более крупные модели (см. раздел «Когда использовать TPU»). У нас модель поменьше, так что особенно интересно посмотреть, даст ли TPU какое-нибудь преимущество.

Для всех моделей мы сравнили скорость обучения на одном Cloud TPU с одним графическим процессором Nvidia P100 и V100. Нужно заметить, что полноценное сравнение должно включать в себя сравнение окончательного качества и сходимости моделей, а не просто пропускную способность. Наши эксперименты — это лишь поверхностные первые бенчмарки, а подробный анализ оставим на будущее.

Тесты для TPU и P100 запускались на инстансах n1-standard-16 платформы Google Cloud (16 виртуальных CPU Intel Haswell, память 60 ГБ). Для графического процессора V100 использовались инстансы p3.2xlarge на AWS (8 виртуальных CPU, 60 ГБ памяти). Все системы под Ubuntu 16.04. Для TPU установили TensorFlow 1.6.0-rc1 из репозитория PyPi. Тесты для GPU запускались из контейнеров nvidia-docker с образами TensorFlow 1.5 (tensorflow:1.5.0-gpu-py3), включающими поддержку CUDA 9.0 и cuDNN 7.0.

TPU-оптимизированные модели

Посмотрим сначала на производительность моделей, которые официально оптимизированы для TPU. Ниже показана производительность по количеству обрабатываемых изображений в секунду.

Размеры пакетов: 1024 на TPU и 128 на GPU. Для последних взяли реализацию из репозитория бенчмарков TensorFlow. В качестве данных для обучения — симуляция набора данных ImageNet от Google в облачном хранилище (для TPU) и на локальных дисках (для GPU)

На ResNet-50 один тензорный процессор Cloud TPU (8 ядер и 64 ГБ ОЗУ) были примерно в 8,4 раза быстрее, чем один P100, и примерно в 5,1 раза быстрее, чем V100. Для InceptionV3 разница в производительности почти такая же (

4,8, соответственно). На вычислениях с меньшей точностью (fp16) V100 значительно прибавляет в скорости.

Понятно, что кроме скорости нужно учитывать и цену. В таблице показана производительность, нормализованная по цене с ежесекундным биллингом. TPU всё равно явно выигрывает.

Кастомные модели LSTM

Наша кастомная модель — это двунаправленная LSTM для классификации текста с 1024 скрытыми юнитами. LSTM являются основными строительными блоками в современных нейросетях, так что это хорошее дополнение для официальных моделей машинного зрения.

Оригинальный код уже использовал фреймворк Estimator, так что очень легко адаптировать его для TPUEstimator. Хотя есть одна большая оговорка: на TPU мы не смогли добиться сходимости модели, хотя та же модель (размер пакетов и прочее) на GPU работала нормально. Думаем, это из-за какого-то бага, который будет исправлен — либо в нашем коде (если найдёте его, сообщите нам!), либо в TensorFlow.

Оказалось, что TPU обеспечивает даже бóльшую прибавку в производительности на модели LSTM (21402 образца/с): в

12,9 раза быстрее, чем Р100 (1658 образцов/с) и в

7,7 раза быстрее, чем V100 (2778 образцов/с)! Учитывая, что модель сравнительно небольшая и никак не оптимизировалась, это очень многообещающий результат. Но пока баг не исправлен, эти результаты будем считать предварительными.

Вывод

На протестированных моделях TPU очень хорошо проявили себя как по производительности, так и с точки зрения экономии денег, по сравнению с последними поколениями GPU. Это противоречит предыдущим оценкам.

Результаты предыдущих бенчмарков. Источник: Forbes

Хотя Google продвигает TPU как оптимальное решение для масштабирования больших моделей, наши предварительные результаты на маленькой модели оказались очень многообещающими. В целом, опыт использования TPU и адаптации кода TensorFlow уже неплох для бета-версии.

Мы считаем, что когда TPU станут доступны более широкой аудитории, то могут стать реальной альтернативой Nvidia GPU.

Бесплатные тензорные процессоры от Google в облаке Colaboratory

Недавно Google предоставил бесплатный доступ к своим тензорным процессорам (tensor processing unit, TPU) на облачной платформе для машинного обучения Colaboratory. Тензорный процессор — это специализированная интегральная схема (ASIC), разработанная Google для задач машинного обучения с использованием библиотеки TensorFlow. Я решил попробовать обучить на TPU сверточную сеть на Keras, которая распознает объекты на изображениях CIFAR-10. Полный код решения можно посмотреть и запустить в ноутбуке.

Фото cloud.google.com

Тензорные процессоры

На Хабре уже писали о том, как устроены TPU (здесь, здесь и здесь), а также почему TPU хорошо подходят для обучения нейронных сетей. Поэтому я не буду углубляться в детали архитектуры TPU, а рассмотрю только те особенности, которые нужно учитывать при обучении нейонных сетей.

Сейчас есть три поколения тензорных процессоров, производительность TPU последнего, третьего поколения составляет 420 TFlops (триллионов операций с плавающей точкой в секунду), он содержит 128 ГБ памяти High Bandwidth Memory. Однако на Colaboratory доступны только TPU второго поколения, у которых 180 TFlops производительности и 64 ГБ памяти. В дальнейшем я буду рассматривать именно эти TPU.

Тензорный процессор состоит из четырех чипов, каждый из которых содержит два ядра, всего в TPU восемь ядер. Обучение на TPU ведется параллельно на всех ядрах с помощью репликации: на каждом ядре работает копия графа TensorFlow с одной восьмой объема данных.

Основа тензорного процессора — матричное устройство (matrix unit, MXU). Оно использует хитрую структуру данных систолический массив размером 128х128 для эффективной реализации операций с матрицами. Поэтому, чтобы наиболее полно использовать ресурсы оборудования TPU, размерность мини-выборки или признаков должна быть кратна 128 (источник). Также из-за особенностей системы памяти TPU желательно, чтобы размерность мини-выборки и признаков была кратна 8.

Платформа Colaboratory

Colaboratory — это облачная платформа от Google для продвижения технологий машинного обучения. На ней можно получить бесплатно виртуальную машину с установленными популярными библиотеками TensorFlow, Keras, sklearn, pandas и т.п. Самое удобное, что на Colaboratory можно запускать ноутбуки, похожие на Jupyter. Ноутбуки сохраняются на Google Drive, можно их распространять и даже организовать совместную работу. Вот так выглядит ноутбук на Colaboratory (картинка кликабельна):

Вы пишите код в браузере в ноутбуке, он выполняется на виртуальной машине в облаке Google. Машина выдается вам на 12 часов, после этого она останавливается. Однако ничто не мешает вам запустить еще одну виртуальную машину и работать еще 12 часов. Только имейте в виду, что после остановки виртуальной машины все данные с нее удаляются. Поэтому не забывайте сохранять нужные данные на свой компьютер или Google Drive, а после перезапуска виртуальной машины загружать заново.

Подробные инструкции по работе на платформе Colaboratory есть здесь, здесь и здесь.

Подключаем тензорный процессор на Colaboratory

После выбора типа ускорителя виртуальная машина, к которой подключается ноутбук Colaboratory, перезапустится и станет доступен TPU.

Если вы загружали на виртуальную машину какие-то данные, то в процессе перезапуска они будут удалены. Придется загружать данные заново.

Нейронная сеть на Keras для распознавания CIFAR-10

В качестве примера попробуем обучить на TPU нейронную сеть на Keras, которая распознает изображения из набора данных CIFAR-10. Это популярный набор данных, содержащий небольшие изображения объектов 10 классов: самолет, автомобиль, птица, кот, олень, собака, лягушка, лошадь, корабль и грузовик. Классы не пересекаются, каждый объект на картинке принадлежит только одному классу.

Загружаем набор данных CIFAR-10 средствами Keras:

Для создания нейронной сети я завел отдельную функцию. Мы будем создавать одинаковую модель два раза: первый вариант модели для TPU, на котором будем обучать, а второй для CPU, где будем распознавать объекты.

Пока на TPU нельзя использовать оптимизаторы Keras, поэтому при компиляции модели указывается оптимизатор из TensorFlow.

Создаем модель Keras для CPU, которую на следующем этапе преобразуем в модель для TPU:

Конвертируем нейросеть на Keras в модель для TPU

Модели на Keras и TensorFlow можно обучать на GPU без каких-либо изменений. На TPU пока так делать нельзя, поэтому придется преобразовать созданную нами модель в модель для TPU.

Для начала нужно узнать, где находится доступный нам TPU. На платформе Colaboratory это можно сделать следующей командой:

Теперь можно получить модель для TPU с помощью функции keras_to_tpu_model :

В первой строке включено логирование на уровне Info. Вот что в логе конвертации модели:

INFO:tensorflow:Querying Tensorflow master (b’grpc://10.102.233.146:8470′) for TPU system metadata.

INFO:tensorflow:Found TPU system:

INFO:tensorflow:*** Num TPU Cores: 8

INFO:tensorflow:*** Num TPU Workers: 1

INFO:tensorflow:*** Num TPU Cores Per Worker: 8

.

WARNING:tensorflow:tpu_model (from tensorflow.contrib.tpu.python.tpu.keras_support) is experimental and may change or be removed at any time, and without warning.

Можно видеть, что найден TPU по указанному нами ранее адресу, в нем 8 ядер. Также мы видим предупреждение, что tpu_model является экспериментальной и может быть изменена или удалена в любое время. Надеюсь, что со временем можно будет обучать модели Keras напрямую на TPU без всякого преобразования.

Обучаем модель на TPU

Модель для TPU можно обучать обычным для Keras образом с помощью вызова метода fit :

Какие здесь особенности. Мы помним, что для эффективного использования TPU размер мини-выборки должен быть кратен 128. Кроме того, на каждом ядре TPU выполняется обучение с использованием одной восьмой всех данных в мини-выборке. Поэтому размер мини-выборки при обучении задаем в 128*8, получается по 128 картинок для каждого ядра TPU. Можно использовать больший размер, например, 256 или 512, тогда производительность будет выше.

В моем случае на обучение одной эпохи требуется в среднем 6 с.

Доля верных ответов на данных для обучения составила 90,06%. Проверяем качество на тестовых данных используя TPU:

Доля верных ответов на тестовых данных: 80.79%

Теперь сохраним веса обученной модели:

TensorFlow выдаст нам сообщение, что веса переданы с TPU на CPU:

INFO:tensorflow:Copying TPU weights to the CPU

Следует отметить, что веса обученной сети сохранились на диск виртуальной машины Colaboratory. Когда виртуальная машина будет остановлена, то все данные с нее сотрутся. Если вы не хотите терять обученные веса, то сохраните их на свой компьютер:

Распознаем объекты на CPU

Теперь давайте попробуем использовать модель, обученную на TPU, для того, чтобы распознавать объекты на изображениях с помощью CPU. Для этого создаем модель заново и загружаем в нее обученные на TPU веса:

Модель готова к использования на центральном процессоре. Давайте попробуем распознать с ее помощью одно из изображений тестового набора CIFAR-10:

Картинка маленькая, но можно понять, что это самолет. Запускаем распознавание:

Получаем список выходных значений нейронов, почти все из них близки к нулю, кроме первого значения, которое соответствует самолету.

[[9.81738389e-01 2.91262069e-07 1.82225723e-02 9.78524668e-07

5.89265142e-07 6.76223244e-10 1.03252004e-10 9.23009047e-09

3.71878523e-05 3.16599618e-08]]

самолет

Распознавание прошло успешно!

Итоги

Удалось продемонстрировать работоспособность TPU на платформе Colaboratory, его вполне можно применять для обучения нейронных сетей на Keras. Однако набор данных CIFAR-10 слишком маленький, его недостаточно для полной загрузки ресурсов TPU. Ускорение по сравнению с GPU получилось небольшим (можете проверить сами выбрав в качеству ускорителя GPU вместо TPU и переобучив модель заново).

На Хабре есть статья, в которой измеряли производительность TPU и GPU V100 на обучении сети ResNet-50. На этой задаче TPU показал такую же производительность, как и четыре GPU V100. Приятно, что Google дает такой мощный ускоритель обучения нейронных сетей бесплатно!

Видео с демонстрацией обучения нейросети Keras на TPU.

Аппаратное ускорение глубоких нейросетей: GPU, FPGA, ASIC, TPU, VPU, IPU, DPU, NPU, RPU, NNP и другие буквы

14 мая, когда Трамп готовился спустить всех собак на Huawei, я мирно сидел в Шеньжене на Huawei STW 2019 — большой конференции на 1000 участников — в программе которой были доклады Филипа Вонга, вице-президента по исследованиям TSMC по перспективам не-фон-неймановских вычислительных архитектур, и Хенга Ляо, Huawei Fellow, Chief Scientist Huawei 2012 Lab, на тему разработки новой архитектуры тензорных процессоров и нейропроцессоров. TSMC, если знаете, делает нейроускорители для Apple и Huawei по технологии 7 nm (которой мало кто владеет), а Huawei по нейропроцессорам готова составить серьезную конкуренцию Google и NVIDIA.

Google в Китае забанен, поставить VPN на планшет я не удосужился, поэтому патриотично пользовался Яндексом для того, чтобы смотреть, какая ситуация у других производителей аналогичного железа, и что вообще происходит. В общем-то за ситуацией я следил, но только после этих докладов осознал, насколько масштабна готовящаяся в недрах компаний и тиши научных кабинетов революция.

Только в прошлом году в тему было вложено больше 3 миллиардов долларов. Google уже давно объявил нейросети стратегическим направлением, активно строит их аппаратную и программную поддержку. NVIDIA, почувствовав, что трон зашатался, вкладывает фантастические усилия в библиотеки ускорения нейросетей и новое железо. Intel в 2016 году потратил 0,8 миллиарда на покупку двух компаний, занимающихся аппаратным ускорением нейросетей. И это при том, что основные покупки еще не начались, а количество игроков перевалило за полсотни и быстро растет.

TPU, VPU, IPU, DPU, NPU, RPU, NNP — что все это означает и кто победит? Попробуем разобраться. Кому интересно — велкам под кат!

Disclaimer: Автору приходилось полностью переписывать алгоритмы обработки видео для эффективной реализации на ASIC, причем клиенты делали прототипирование на FPGA, поэтому представление о глубине разницы архитектур есть. Однако, непосредственно с железом в последнее время автор не работал. Но предчувствует, что вникать придется.

Предпосылки проблем

Количество требуемых вычислений бурно растет, народ с удовольствием взял бы больше слоев, больше вариантов архитектуры, активнее поигрался бы с гиперпараметрами, но… упирается в производительность. При этом, например, с ростом производительности старых добрых процессоров — большие проблемы. Все хорошее когда-нибудь заканчивается: закон Мура, как известно, иссякает и скорость роста производительности процессоров падает:

Расчеты реальной производительности целочисленных операций по SPECint по сравнению с VAX11-780, здесь и далее часто логарифмическая шкала

Если с середины 80-х по середину 2000-х — в благословенные годы расцвета компьютеров — рост шел со скоростью в среднем 52% в год, то последние годы он сократился до 3% в год. И это — проблема (перевод недавней статьи патриарха темы Джона Хеннесси о проблемах и перспективах современных архитектур был на Хабре).

Причин много, например, перестала расти частота процессоров:

Сложнее стало уменьшать размер транзисторов. Последняя напасть, кардинально снижающая производительность (в том числе — производительность уже выпущенных CPU) — это (барабанная дробь)… правильно, безопасность. Meltdown, Spectre и другие уязвимости наносят колоссальный ущерб скорости роста вычислительной мощности CPU (пример отключения hyperthreading(!)). Тема стала популярна, и новые уязвимости такого рода находят практически ежемесячно. И это — кошмар какой-то, поскольку больно бьет по производительности.

При этом развитие многих алгоритмов прочно завязано на ставший привычным рост мощности процессоров. Например, очень многие исследователи сегодня не парятся о скорости алгоритмов — что-нибудь да придумают. И ладно бы при обучении — сети становятся большими и «тяжелыми» для использования. Особенно это ярко видно на видео, для которого большинство подходов в принципе не применимы с высокой скоростью. А они имеют смысл часто только в реальном времени. Это тоже проблема.

Аналогично, сейчас развиваются новые стандарты сжатия, которые предполагают увеличение мощности декодеров. А если мощность процессоров не будет расти? Старшее поколение помнит, как в 2000-х возникали проблемы проиграть видео высокого разрешения в свежем тогда H.264 на старых компьютерах. Да, качество было лучше при меньшем размере, но на быстрых сценах картинка подвисала или звук рвался. Мне приходится общаться с разработчиками нового VVC/H.266 (релиз планируется на следующий год). Им не позавидуешь.

Итак, что век грядущий нам готовит в свете уменьшения скорости роста производительности процессоров в приложении к нейросетям?

Обычный CPU — это замечательная числодробилка, которую совершенствовали десятилетия. Увы, под другие задачи.

Когда мы работаем с нейросетями, особенно глубокими, у нас непосредственно сеть может занимать сотни мегабайт. К примеру, требования к памяти сетей обнаружения объектов такие:

| model | input size | param memory | feature memory |

| rfcn-res50-pascal | 600 x 850 | 122 MB | 1 GB |

| rfcn-res101-pascal | 600 x 850 | 194 MB | 2 GB |

| ssd-pascal-vggvd-300 | 300 x 300 | 100 MB | 116 MB |

| ssd-pascal-vggvd-512 | 512 x 512 | 104 MB | 337 MB |

| ssd-pascal-mobilenet-ft | 300 x 300 | 22 MB | 37 MB |

| faster-rcnn-vggvd-pascal | 600 x 850 | 523 MB | 600 MB |

По нашему опыту коэффициенты глубокой нейросети для обработки полупрозрачных границ могут занимать 150–200 Мб. У коллег в нейросети определения возраста и пола размер коэффициентов порядка 50 Мб. И при оптимизации для мобильной версии пониженной точности — порядка 25 Мб (float32⇒float16).

При этом график задержки при обращении к памяти в зависимости от размера данных распределяется примерно так (масштаб по горизонтали логарифмический):

Т.е. при увеличении объема данных больше 16 Мб задержка возрастает в 50 и более раз, что фатально сказывается на производительности. Фактически большую часть времени CPU при работе с глубокими нейросетями тупо ждет данных. Интересны данные Intel по ускорению разных сетей, где, фактически, ускорение идет, только когда сеть становится маленькой (например, в результате квантования весов), чтобы начать хотя бы частично входить в кэш вместе с обрабатываемыми данными. Заметим, что кэш современного CPU потребляет до половины энергии процессора. В случае тяжелых нейросетей он оказывается малоэффективен и работает неразумно дорогим обогревателем.

Тема хорошо известна, поэтому бегло обозначим главное. У GPU в случае нейросетей существенное преимущество по производительности на массивно-параллельных задачах:

Обратите внимание, как отжигают 72-ядерный Xeon Phi 7290, при том, что «синий» — это тоже серверный Xeon, т.е. Intel так просто не сдается, о чем ниже еще будет. Но важнее то, что память у видеокарт изначально рассчитана под примерно в 5 раз более высокую производительность. В нейросетях вычисления с данными крайне простые. Несколько элементарных действий, и нам нужны новые данные. Как следствие, скорость доступа к данным является критичной для эффективной работы нейросети. Высокоскоростная память «на борту» GPU и более гибкая система управления кэш-памятью, чем на CPU, позволяет решить эту проблему:

Тим Детмерс уже несколько лет поддерживает интересный обзор «Which GPU(s) to Get for Deep Learning: My Experience and Advice for Using GPUs in Deep Learning» («Какой GPU лучше для глубокого обучения. »). Понятно, что для обучения рулят Теслы и Титаны, хотя разница архитектур может вызывать интересные всплески, например, в случае рекуррентных нейросетей (а лидер вообще TPU, заметим на будущее):

Однако, там есть крайне полезный график производительности за доллар, где на коне RTX (скорее всего за счет их Tensor cores), если вам её памяти хватает, конечно:

Безусловно, стоимость вычислений важна. Второе место первого рейтинга и последнее второго — Tesla V100 продается за 700 тысяч рублей, как 10 «обычных» компов (+ недешевый Infiniband коммутатор, если хочется обучать на нескольких узлах). Правда V100 и работает за десятерых. Люди готовы переплачивать за ощутимое ускорение обучения.

FPGA — это уже интереснее. Это сеть из нескольких миллионов программируемых блоков, которые мы можем также программно соединять между собой. Сеть и блоки выглядят как-то так (тонкое место — Bottleneck, обратите внимание, опять перед памятью чипа, но все полегче, о чем будет ниже):

Естественно, применять FPGA имеет смысл уже на этапе применения нейросети (для обучения в большинстве случаев маловато памяти). Причем тема выполнения на FPGA сейчас начала активно развиваться. Например, вот фреймворк fpgaConvNet, помогающий заметно ускорить применение CNN на FPGA и снизить при этом энергопотребление.

Ключевой плюс FPGA в том, что мы можем хранить сеть непосредственно в ячейках, т.е. тонкое место в виде перегоняемых 25 раз в секунду (для видео) в одном и том же направлении сотен мегабайт одних и тех же данных волшебным образом пропадает. Что позволяет при более низкой тактовой частоте и отсутствии кэшей вместо понижения производительности получить заметное повышение. Да еще и кардинально снизить глобальное потепление энергопотребление на единицу вычислений.

К процессу активно подключился Intel, выпустив в прошлом году в открытых исходниках OpenVINO Toolkit, включающий в себя Deep Learning Deployment Toolkit (часть OpenCV). Причем производительность на FPGA на разных сетках выглядит довольно интересно, и преимущество у FPGA по сравнению с GPU (правда интегрированным GPU от Intel) весьма существенное:

Что особо греет душу автору — сравниваются FPS, т.е. кадры в секунду — наиболее практическая метрика для видео. С учетом того, что Intel в 2015 году купил второго по размеру игрока на рынке FPGA, компанию Altera, график дает хорошую пищу для размышлений.

И, очевидно, входной барьер в подобные архитектуры выше, поэтому должно пройти некоторое время, чтобы появились удобные инструменты, эффективно учитывающие принципиально иную архитектуру FPGA. Но недооценивать потенциал технологии не стоит. Уж больно много тонких мест она расшивает.

Напоследок подчеркнем, что программирование FPGA — это отдельное искусство. Как таковая программа там не выполняется, а все вычисления идут в терминах потоков данных, задержек потоков (что влияет на производительность) и использованных гейтов (которых всегда не хватает). Поэтому чтобы начать эффективно программировать — нужно основательно поменять собственную прошивку (в той нейросети, которая между ушами). С хорошей эффективностью это получается не у всех. Впрочем, новые фреймворки скоро скроют от исследователей внешнюю разницу.

Далее идет ASIC — это сокращение от Application-Specific Integrated Circuit, т.е. интегральная схема под нашу задачу. Например, реализующая положенную в железо нейросеть. При этом большинство вычислительных узлов может работать параллельно. Фактически только зависимости по данным и неравномерность вычислений на разных уровнях сети могут помешать нам постоянно задействовать работающими все ALU.

Пожалуй, наибольшую рекламу ASIC среди широкой публики в последние годы сделал майнинг криптовалют. В самом начале майнинг на CPU был вполне рентабелен, позднее пришлось покупать GPU, потом — FPGA, а потом — специализированные ASIC, благо народ (читай — рынок) созрел для заказов, при которых их производство стало рентабельным.

В нашей области тоже уже появились (естественно!) сервисы, помогающие положить нейросеть на железо с необходимыми характеристиками по энергопотреблению, FPS и цене. Волшебно, согласитесь!

НО! Мы теряем настраиваемость сети. И, естественно, люди об этом тоже думают. Например, вот статья с говорящим названием «Can a reconfigurable architecture beat ASIC as a CNN accelerator?» («Может ли конфигурируемая архитектура побить ASIC, как акселератор CNN?»). Работ на эту тему хватает, ибо вопрос не праздный. Основной минус ASIC в том, что после того, как мы загнали сеть в железо, нам становится сложно ее поменять. Наиболее выгодны они для случаев, когда уже хорошо отлаженная сеть нам нужна миллионами чипов с низким энергопотреблением и высокой производительностью. И такая ситуация постепенно складывается на рынке автопилотов машин, например. Или в камерах видеонаблюдения. Или в камерах роботов-пылесосов. Или в камерах домашнего холодильника. Или в камере кофеварки. Или в камере утюга. Ну вы поняли идею, короче!

Важно, что при массовом производстве чип стоит дешево, работает быстро и потребляет минимум энергии.

Напомним, при работе сетей есть две задачи — это обучение (training) и выполнение (inference). Если FPGA/ASIC ориентированы в первую очередь на ускорение выполнения (в том числе какой-то фиксированной сети), то TPU (Tensor Processing Unit или тензорные процессоры) — это либо аппаратное ускорение обучения, либо относительно универсальное ускорение работы произвольной сети. Название красивое, согласитесь, хотя по факту пока используются тензоры ранга 2 c Mixed Multiply Unit (MXU) соединенных с высокоскоростной памятью (High-Bandwidth Memory — HBM). Ниже схема архитектуры от TPU Google 2-й и 3-й версии:

TPU Google

Вообще рекламу названию TPU сделала Google, раскрыв внутренние разработки в 2017 году:

Предварительные работы по специализированным процессорам для нейросетей они начали с их слов еще в 2006, в 2013 создали проект с хорошим финансированием, а в 2015 начали работать с первыми чипами, которые сильно помогли с нейросетями для облачного сервиса Google Translate и не только. И это было, подчеркнем, ускорение выполнения сети. Важным преимуществом для дата-центров является на два порядка более высокая энергоэффективность TPU по сравнению с CPU (график для TPU v1):

Также, как правило, по сравнению с GPU в 10–30 раз в лучшую сторону отличается производительность выполнения сети:

Разница даже в 10 раз существенна. Понятно, что разница с GPU в 20–30 раз определяет развитие этого направления.

И, к счастью, Google не одинок.

TPU Huawei

Ныне многострадальный Huawei также начал разработку TPU несколько лет назад под именем Huawei Ascend, причем сразу в двух версиях — для дата-центров (как Google) и для мобильных устройств (что Google тоже начал делать недавно). Если верить материалам Huawei, то они обогнали свежий Google TPU v3 по FP16 в 2,5 раза и NVIDIA V100 в 2 раза:

Как обычно хороший вопрос: как этот чип поведет себя на реальных задачах. Ибо на графике, как видим, пиковая производительность. Кроме того, Google TPU v3 хорош во многом тем, что умеет эффективно работать в кластерах по 1024 процессора. Huawei тоже заявила серверные кластера для Ascend 910, но подробностей нет. В целом инженеры Huawei показывают себя крайне грамотными последние 10 лет, и есть все шансы, что в 2,8 раз большая пиковая производительность по сравнению с Google TPU v3 вкупе с новейшим техпроцессом 7 nm будут использованы по делу.

Критичным для производительности являются память и шина данных, и по слайду видно, что внимание этим компонентам уделено значительное (в том числе скорость общения с памятью заметно быстрее, чем у GPU):

Также в чипе идет несколько другой подход — масштабируются не двумерные MXU 128×128, а вычисления в трехмерном кубе меньшего размера 16х16хN, где N=<16,8,4,2,1>. Поэтому ключевой вопрос — насколько хорошо это ляжет на реальное ускорение конкретных сетей (например, вычисления в кубе удобны для изображений). Также, при внимательном изучении слайда видно, что в отличие от Google в чип сразу закладывается работа со сжатым FullHD видео. Для автора это звучит очень обнадеживающе!

Как упоминалось выше, в той же линейке разрабатываются процессоры для мобильных устройств, для которых критична энергоэффективность, и на которых сеть будет в основном выполняться (т.е. отдельно — процессоры для облачного обучения и отдельно — для выполнения):

И по этому параметру все смотрится неплохо по сравнению с NVIDIA по крайней мере (заметим, что с Google они сравнение не привели, правда, Google в руки облачные TPU не дает). А их мобильные чипы будут конкурировать с процессорами от Apple, Google и других компаний, но тут пока рано подводить итоги.

Хорошо видно, что новые чипы Nano, Tiny и Lite должны быть еще лучше. Становится понятно, чего испугался Трамп почему многие производители внимательно изучают успехи Huawei (обогнавшей по выручке все компании-производители железа в США, включая Intel в 2018 году).

Аналоговые глубокие сети

Как известно — техника часто развивается по спирали, когда на новом витке актуальными становятся старые и забытые подходы.

Нечто подобное вполне может произойти с нейросетями. Вы, возможно, слышали, что когда-то операции умножения и сложения выполнялись электронными лампами и транзисторами (например, преобразование цветовых пространств — типичное перемножение матриц — было в каждом цветном телевизоре до середины 90-х)? Возник хороший вопрос: если уж наша нейронная сеть относительно устойчива к неточным вычислениям внутри, что если мы переведем эти вычисления в аналоговый вид? Мы с ходу получаем заметное ускорение вычислений и потенциально кардинальное снижение расхода энергии на выполнение одной операции:

При таком подходе DNN (Deep Neural Network) вычисляется быстро и энергоэффективно. Но есть проблема — это ЦАП/АЦП (DAC/ADC) — преобразователи из цифры в аналог и обратно, которые уменьшают и энергоэффективность, и точность процесса.

Впрочем, еще в 2017 году в IBM Research предложили аналоговые CMOS для RPU (Resistive Processing Units), которые позволяют хранить обрабатываемые данные также в аналоговом виде и существенно повысить общую эффективность подхода:

Также, помимо аналоговой памяти сильно может помочь снижение точности нейросети — это ключ к миниатюризации RPU, а значит, к увеличению числа вычислительных ячеек на кристалле. И здесь IBM также в лидерах, а частности недавно в этом году они вполне успешно до 2-битной точности огрубили сеть и собираются довести точность до однобитной (и двухбитной при тренировках), что потенциально позволит в 100 раз (!) поднять производительность по сравнению с современными GPU:

Говорить предметно про аналоговые нейрочипы пока рано, поскольку пока всё это тестируется на уровне ранних прототипов:

Однако, потенциально направление аналоговых вычислений выглядит предельно интересно.

Единственное, что смущает — что это IBM, подавшая уже десятки патентов по теме. По опыту, в силу особенностей корпоративной культуры, они относительно слабо кооперируются с другими компаниями и, владея какой-то технологией, скорее склонны затормозить ее развитие у других, чем эффективно поделиться. Например, IBM в свое время отказались лицензировать арифметическое сжатие для JPEG комитету ISO при том, что в драфте стандарта был вариант с арифметическим сжатием. В итоге JPEG ушел в жизнь со сжатием по Хаффману и жал на 10–15% хуже, чем мог бы. Та же ситуация была со стандартами сжатия видео. А индустрия массово перешла на арифметическое сжатие в кодеках только когда 5 патентов IBM истекли 12 лет спустя… Будем надеяться, что в IBM будут более склонны к кооперации в этот раз, и, соответственно, пожелаем максимальных успехов в области всем, кто не связан с IBM, благо таких людей и компаний немало.

Если получится — это будет революция в применении нейросетей и переворот во многих областях computer science.

Разные другие буквы

Вообще, тема ускорения нейросетей стала модной, ей занимаются все крупные компании и десятки стартапов, и как минимум 5 из них привлекли более 100 миллионов долларов инвестиций к началу 2018 года. Всего же в 2017 в стартапы, связанные с разработкой чипов, было инвестировано 1,5 МИЛЛИАРДА долларов. При том, что инвесторы не замечали чипмейкеров добрых 15 лет (ибо ловить там на фоне гигантов было нечего). В общем — сейчас появился реальный шанс на небольшую железную революцию. Причем предсказать, какая архитектура победит крайне сложно, необходимость в революции назрела, а возможности в увеличении производительности велики. Созрела классическая революционная ситуация: Мур уже не может, а Дин еще не готов.

Ну а поскольку важнейший рыночный закон — отличайся, появилось много новых букв, например:

Здесь и далее в этом разделе будут приведены в основном слайды корпоративных презентаций в качестве примеров самоназваний технологий

Понятно, что прямое сравнение проблематично, но вот любопытные данные, сравнивающие чипы с нейропроцессорами от Apple и Huawei, производимые упоминавшейся в начале TSMC. Видно, что соревнование идет жесткое, новое поколение показывает прирост производительности в 2-8 раз и усложнение технологических процессов:

И это перечислены только наиболее крупные направления, в развитие которых вложены сотни миллионов (при разработке железа это важно).

В общем, как видим, бурно расцветают все цветы. Постепенно компании переварят миллиарды долларов инвестиций (обычно на производство чипов требуется 1,5–3 года), пыль осядет, лидер станет понятен, победители, как обычно, напишут историю, и название наиболее успешной на рынке технологии станет общепринятым. Так уже было не раз («IBM PC», «Smartphone», «ксерокс» и т.д.).

Пара слов про корректное сравнение

Как уже было замечено выше, корректно сравнивать производительность нейросетей непросто. Ровно поэтому Google публикует график, на котором TPU v1 делает NVIDIA V100. NVIDIA, видя такое безобразие, публикует график, где Google TPU v1 проигрывает V100. (Дык!) Google публикует следующий график, где V100 с треском проигрывает Google TPU v2 & v3. И, наконец, Huawei — график, где все с треском проигрывают Huawei Ascend, но V100 лучше TPU v3. Цирк, короче. Что характерно — своя правда есть в каждом графике!

Первопричины ситуации понятны:

Поскольку в авторах там один из основных контрибьюторов TensorFlow, есть все шансы узнать, на чем быстрее всего обучать и, возможно, использовать (ибо мобильную версию TF со временем скорее всего в этот тест также включат).

Недавно международная организация IEEE, издающая третью часть мировой технической литературы по радиоэлектронике, компьютерам и электротехнике, не по-детски забанила Huawei, вскоре, впрочем, отменив бан. В текущем рейтинге MLPerf Huawei пока отсутствует, при том Huawei TPU является серьезным конкурентом Google TPU и карт NVIDIA (т.е. помимо политических, есть и экономические причины игнорировать Huawei, скажем прямо). С нескрываемым интересом будем следить за развитием событий!

Все в небо! Ближе к облакам!

И, раз уж речь пошла об обучении, стоит несколько слов сказать про его специфику:

Например, господа из IBM Research полны оптимизма, разработать спец-чипы, которые уже через 5 лет на порядок поднимут эффективность вычислений (а через 10 лет на 2 порядка, достигнув увеличения в 1000 раз по сравнению с уровнем 2016 года, на данном графике, правда, в эффективности на ватт, но мощность ядер при этом тоже вырастет):

Все это означает появление железок, обучение на которых будет относительно быстрым, но стоить которые будут дорого, что естественным образом приводит к идее разделять время использования этой дорогой железки между исследователями. А эта идея сегодня не менее естественно приводит нас к облачным вычислениям. И переход обучения в облака уже давно активно идет.

Заметим, что уже сейчас обучение одних и тех же моделей может отличаться по времени на порядок у разных облачных сервисов. Ниже лидирует Amazon, а на последнем месте бесплатный Colab от Google. Обратите внимание, как изменяется результат от количества V100 у лидеров — увеличение числа карт в 4 раза(!) повышает производительность менее, чем на треть (. ) — с голубого до фиолетового, а у Google и того меньше:

Похоже, в ближайшие годы различие вырастет до двух порядков. Господа! Готовим деньги! Будем дружно возвращать многомиллиардные инвестиции наиболее успешным инвесторам…

Если кратко

| Тип | Что ускоряет | Комментарий |

| CPU | В основном выполнение | Обычно худшие по скорости и энергоэффективности, но вполне пригодны для выполнения небольших по размеру нейросетей |

| GPU | Выполнение+ обучение | Наиболее универсальное решение, но довольно дорогое, как по стоимости вычислений, так и по энергоэффективности |

| FPGA | Выполнение | Относительно универсальное решение для исполнения сетей, в некоторых случаях позволяет кардинально ускорить выполнение |

| ASIC | Выполнение | Наиболее дешевый, быстрый и энергоэффективный вариант исполнения сети, но нужны большие тиражи |

| TPU | Выполнение+ обучение | Первые версии использовались для ускорения выполнения, сейчас используются для весьма эффективного ускорения выполнения и обучения |

| IPU, DPU… NNP | В основном обучение | Много маркетинговых букв, которые благополучно забудут в ближайшие годы. Основной плюс этого зоопарка — проверка разных направлений ускорения DNN |

| Analog DNN / RPU | Выполнение+ обучение | Потенциально аналоговые ускорители могут произвести революцию в скорости и энергоэффективности выполнения и обучения нейросетей |

Пара слов про программное ускорение

Справедливости ради упомянем, что сегодня большая тема — программное ускорение выполнения и обучения глубоких нейросетей. Выполнение можно заметно ускорить в первую очередь за счет так называемого квантования сети. Возможно это, во-первых, поскольку используемый диапазон значений весов не так велик и зачастую можно огрубить значения весов с 4-байтового значения с плавающей точкой до 1 байтового целого (и, вспоминая успехи IBM, даже сильнее). Во-вторых, обученная сеть в целом довольно устойчива к шуму в вычислениях и точность работы при переходе к int8 падает незначительно. При этом, несмотря на то, что количество операций может даже возрасти (за счет масштабирования при счете), то, что сеть уменьшается в размере в 4 раза и может считаться быстрыми векторными операциями ощутимо поднимает общую скорость выполнения. Особенно это важно для мобильных приложений, но и в облаках вполне работает (пример ускорения выполнения в облаках Amazon):

Есть и другие способы алгоритмического ускорения выполнения сети и еще больше способов ускорения обучения. Впрочем, это отдельные большие темы, про которые не в этот раз.

Вместо заключения

В своих лекциях инвестор и автор Тони Себа приводит великолепный пример: в 2000 году суперкомпьютер №1 производительностью 1 терафлопс занимал 150 квадратных метров, стоил 46 миллионов долларов и потреблял 850 кВт:

15 лет спустя GPU NVIDIA производительностью 2.3 терафлопса (в 2 раза больше) помещался в руке, стоил 59$ (улучшение примерно в миллион раз) и потреблял 15 Вт (улучшение в 56 тысяч раз):

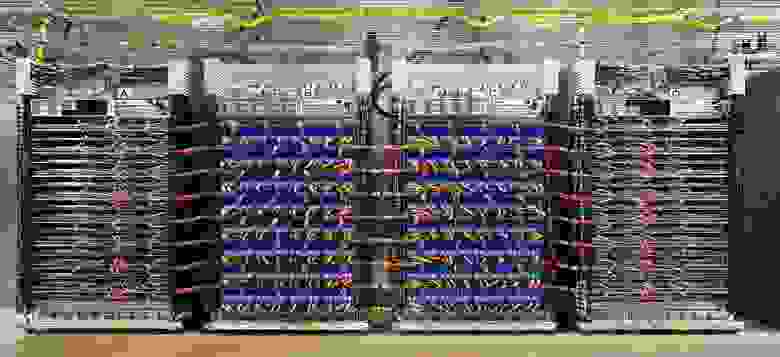

В марте этого года Google представила TPU Pods — фактически суперкомпьютеры с жидкостным охлаждением на основе TPU v3, ключевым свойством которых является то, что они могут работать совместно в системах по 1024 TPU. Выглядят они довольно впечатляюще:

Точные данные не приводятся, но говорится, что система сопоставима с Top-5 суперкомпьютеров мира. TPU Pod позволяет кардинально повысить скорость обучения нейросетей. Для увеличения скорости взаимодействия TPU соединены высокоскоростными магистралями в тороидальную структуру:

Похоже, через 15 лет этот нейропроцессор вдвое большей производительности тоже вполне сможет поместиться в руке, как Skynet processor (согласитесь, чем-то похож):

Кадр из режиссерской версии фильма «Терминатор-2»

Учитывая текущую скорость совершенствования аппаратных акселераторов глубоких нейросетей и пример выше, это совершенно реально. Есть все шансы через несколько лет взять в руку чип, производительностью, как сегодняшний TPU Pod.

Кстати, забавно, что в фильме создатели чипа (видимо, представляя себе, куда может завести сеть самообучение) по умолчанию отключили дообучение. Характерно, что сам T-800 не мог включить training mode и работал в режиме inference mode (см. более длинную режиссерскую версию). Причем его neural-net processor был продвинутым и при включении дообучения мог использовать ранее накопленные данные для обновления модели. Неплохо для 1991 года.

Этот текст был начат в жарком 13-миллионном Шеньжене. Я сидел в одном из 27 000 электротакси города и с большим интересом рассматривал 4 жидкокристаллических экрана машины. Один маленький — среди приборов перед водителем, два — по центру в торпеде и последний — полупрозрачный — в зеркале заднего вида, совмещенный с видеорегистратором, камерой видеонаблюдения салона и андроидом на борту (судя по верхней строке с уровнем заряда и связи с сетью). Там отображались данные водителя (на кого жаловаться, если что), свежий прогноз погоды и, похоже, была связь с таксопарком. Водитель не знал английского, и поспрашивать его про впечатления от электромашины не получилось. Поэтому он лениво давил педаль, чуть продвигая машину в пробке. А я с интересом наблюдал за окном футуристичный вид — китайцы в пиджаках ехали с работы на электросамокатах и моноколесах… и размышлял, как все это будет выглядеть через 15 лет…

Собственно, уже сегодня зеркало заднего вида, пользуясь данными камеры видеорегистратора и аппаратной акселерацией нейросетей, вполне в состоянии управлять машиной в пробке и прокладывать маршрут. Днем, по крайней мере ). Через 15 лет система явно будет не только в состоянии водить машину, но и с удовольствием предоставит мне характеристики свежих китайских электромобилей. На русском, естественно (как вариант: английском, китайском… албанском, наконец). Водитель тут лишнее, слабо обучаемое, звено.

Господа! Нас ждут ПРЕДЕЛЬНО ИНТЕРЕСНЫЕ 15 лет!

UPD: Наиболее интересные комментарии:

Про квантование и ускорение вычислений на FPGA

На FPGA не только арифметика произвольной точности доступна а ещё чертовски важна возможность сохранять и обрабатывать данные произвольной битности. Например в надоевшем всем MobileNetV2 W и B коэффициентов слишком много и их заквантовать можно без особой потери точности только до 16 бит, или же придётся переучивать. Но если внутрь глянуть и собрать статистику по каналам и слоям то можно увидеть что все 16 бит используются только на входе на первых 1000 W коэффициентов, остальные pointwise имеют 8- 11 бит, реально же важны из них только 2-3 старших бита и знак, и статистика использования каналов такая что много каналов где вообще нули, или малые значения, либо каналы где почти все значения 8-11 бит, т.е. можно экспоненту прибить гвоздями в компайлтайме и не хранить т.е. по факту можно сохранить в ROM памяти не 16 битные а 4 битные значения и даже можно вместить на дешёвых FPGA всю нейросеть без особой потери точности (менее 1%), а также обрабатывать на скоростях до десятков тысяч FPS c latency такой что получаем ответ нейросети сразу как заканчивается приём кадра.

Единственная проблема в автоматическом вычислении оптимальной битности и алгоритма сжатия (откидывать, мью закон, насыщать), симуляция RTL уровня дизайна на один кадр всей сетки занимает порядка нескольких десятков секунд, весь валидационный датасет один раз прогнать уже немало времени требует, а перебор параметров становиться вообще долгим. всё руки не доходят сделать транслятор в GCC на AVX256 с точностью вычислений bitperfect (если сравнивать с верилогом FPGA по шагам) и подбирать битность уже с скоростью в десятки и сотни FPS на том же обычном ПК (надо же просто хитро изменять константные сэты W и B, а их использовать может что угодно главное подсчитать быстро).

При вычислении в ряде мест особенно я вообще умудрялся заталкивать в строчный буфер одну только экспоненту и знак! т.к. dephwise чувствительна скорее к нему.

В ряде мест я использовал сжатие звука u-law с редуцированной битностью и сохранением нуля (ЭТО КАПЕЦ ВАЖНО! звуковые кодеки не сохраняют нуль а в сетке нулевых коэф много и они обязаны быть нулями).

Ах да, при вычислениях часто очень хорошо помогает дизеринг в ряде мест, особенно до Релу6, на фпга его реализовать очень просто, а ошибки квантования он сводит на ура.

А так же свои видеопроцессоры особым образом уменьшающие шум дабы предотвратить смычку субпространств в соседнюю область и не дать ложно срабатывать сетке из за шума (всем известные баги сети когда спец шумом можно взломать сеть). Дизеринг — промежуточных результатов вычислений, когда вычисляешь в FixedPoint результат dot product а — в битах как два Fractional part, и на одну дробную часть бит надо сдвинуть — вот тут имеет смысл иногда добавлять дизеринг, а иногда он вреден, а иногда бесполезен например после fc этапа в софтмакс всё равно запрессуется по экспоненте и к мелочам придираться бесполезно.

Что-то похожее пытаются сделать и в рамках проекта TVM в частности ( tvm.ai/about), где стек восстановлен от фронденда (того же самого Keras) и до самого низа. Как я понял, основная новизна этого конкретно проекта — поддержка «высоко»-гетерогенного железа (bare metal, процессоры с кастомным ISA, FPGA и тд.) с уклоном во встраиваемые системы и edge computing. Есть ряд исследовательских групп сформировавшихся вокруг TVM пытающихся прикрутить HLS к TVM как бэкэнд для FPGA. Хороший HLS может сделать парадигму программирование FPGA «ближе» к мировозрению софтварного программиста, и (в идеале) сделать универсальное прототипирование сеток под FPGA так же из коробки, как и под GPU/TPU сейчас.

P.S. Еще FPGA позволяют реализовывать концепцию transparent hardware (и рядом — open-source hardware), что может помочь решить вопросы безопасности и конфиденциальности, что особенно важно если вы оффлоадите свою уникальную модель (да еще и с «деликатными» данными) в облачко на обучение. Но это пока скорее ресерч-ресерч. В общем, FPGA в новом свете современных нагрузок и требований — это реально круто и это направление надо копать

Пять копеек про FPGA, на конец 2019 года несколько производителей ПЛИС анонсировали новые семейства, ориентированные как раз под машинное обучение. Обратите внимание на новшества в архитектуре — появляются блоки спец.вычислителей для нейросетей вместо/в дополнение к dsp-блокам у Xilinx и у Achronix, а также на количество интерфейсов к DDR.

Что касается критики, имхо, она во многом справедлива, FPGA действительно гораздо слабее ASIC-ов. Однако у FPGA есть и очень сильные преимущества: они программируемы и достаточно дёшевы для небольших партий, в то время как на изготовление ASIC требуются месяца и миллионы долларов, запрограммить FPGA может буквально студент на тест-ките за пару сотен долларов. Т.е. порог вхождения в железо гораздо-гораздо ниже для простых смертных. Мне кажется это очень существенным для маленьких стран и для маленьких фирм, ASIC-и, имхо, весьма тяжеловесны в этом плане. Кроме того, время выхода на рынок для изделий на FPGA гораздо быстрее, чем у ASIC.

Далее, в сравнении с CPU, FPGA имеют более высокую производительность для многих задач с параллелизмом уровня данных, но если нужна сложная управляющая логика, то это уже не к ПЛИС в основном.

Имхо, в сравнении с GPU для того же ИИ первоначально казалось, что у FPGA практически не было шансов, но они во многом вырулили: в частности, во-первых энергоэффективностью, здесь они делают GPU легко во многом за счет того, что используют ровно столько сколько надо ресурсов, без оверхедов на питание неиспользуемых, во-вторых даже производительностью (но здесь это часто больше хаки, чем очевидный выигрыш, в частности, уменьшение разрядности операндов, в FPGA это проще простого, а в GPU такие вещи появляются только сейчас, насколько могу судить). В целом, FPGA выглядит очень круто для быстроизменяющихся нестабильных задач, таких как ИИ, если задачи стабилизируются, то можно выкатывать ASIC-и.

По этому пути пошли в датацентрах Microsoft (проект Catapult v.2), сделав там у каждого сервера навесной FPGA-акселератор. Они заявляют, что сейчас это самое крупное вложение в FPGA. И планируют часть стабильной логики (инфраструктуру) впоследствии изготовить в кремнии.

Ещё одной интересной темой в контексте FPGA и ИИ мне кажется всякие программные решения вроде Ristretto и Deephi, которые подрезают нужным образом нейронные сети, а Deephi ещё и генерят под это логику FPGA. Но в целом, я не спец по ИИ, так что может многого ещё не вижу из того, что происходит.

Серьезная проблема FPGA состоит в сложности программирования для нежелезячных программистов и её пытаются решить самые различные стартапы.

Мне думается, что FPGA это вынужденная мера:

они удачно совмещают относительную дешевизну, скорость вычислений и скорость прототипирования и внесения изменений по сравнению с ASIC.

Для примера:

FPGA

Нужно организовать ускорение вычисления (но не обучения), надо несколько рабочих мест (один комплект лицензии квартуса, моделсима, лицензий на IP ядра и сторонних корок стоил 30-50к баксов лет 5 назад когда я их покупал).

надо купить карточек, хотя бы середнячки типа Аррию10 по количеству рабочих мест плюс одну (если сожгут и не ждать), это уже по 5кбаксов*(N+1)

ну и зарплаты, офис, бухгалтерия и прочие расходы — грубо говоря по 10к баксов в месяц на разработчика, работать они явно будут не пару месяцев а пару лет, это уже 120к*N

За это время можно сделать десяток версий (один год делать первую удачную, а потом каждый месяц — полтора вносить правки)

Итого за год: (120+50+5)*N, для 5 человек это 880т баксов

немало но найти желающих оплатить попробовать без гарантий можно

ASIC

Тут я не специалист но мне кажется что софт будет стоить гораздо дороже (оптимистично предположу что в 2 раза)

Заказ чипа стоить будет уже в диапазоне миллиона долларов за одну итерацию

одна итерация от верилога до железа займет в разы больше (3-4 месяца)

в ASIC не закинешь узкоспециализированную сеть с «прибитыми гвоздями» разрядностями и архитектурой нет смысла делать — значит структура станет сложнее: должна быть в меру универсальной, это в разы сложнее

нужны переговорщики, крупный финансовый капитал и имя (в первую очередь завод залезет в кошелёк и если ты мелочь тебя вообще проигнорируют), менеджеры, прочие инженеры тоже нужны — под чип нужна плата и желательно корпус с охлаждением, это очень нетривиального уровня схемотехники и технологии.

вот заметьте: что в том же майнинге платы специально сделаны примитивными — всё постарались затолкать внутрь чипа, включая импульсные регуляторы напряжений, токовые драйверы для интерфейсов и тд и тп.

А это опять таки нужны не простые верилог разработчики а с знанием аналога плюс знания физики полупроводников и технологий (я такое поверхностно изучал в MiT — это ОЧЕНЬ СЛОЖНО, это просто космос и передовой край сплава науки и техники, суровый такой без смузи и единорогов и проповедников от маркетинга стартапов, чистая инженерия и наука)

Итог по асику подсчитать сложно, но это явно десятки миллионов долларов, штат раз в 10 больше по людям и сроки первого выхода глючного но как то работающего уже 3-5 лет, с очень большим риском неудачи (и социальные — заставить работать команду, удержать и вывести к финишу, и технические — не факт что запланированная архитектура выстрелит, и бизнес — не факт что все подрядчики не подведут) и шансов сделать несколько разных попыток с разной архитектурой мало, точнее всего одна попытка: переделывать с нуля никто не даст.

Это дело мега корпораций с! уже! имеющимися наработками и людьми. например NEC и SONY (c ними и олимпусам по бионику работал, примерно краем уха знаю реальные сроки в 10-15 лет на одну самую первую итерацию с нуля, это уже не тайна)

Кратко: FPGA это способ ускорить и удешевить разработку в десятки и сотни раз относительно ASIC.

Хотелось бы сердечно поблагодарить: