vddp voltage ryzen что это

DDR4 и Ryzen. Нюансы настройки и разгона памяти на платформе AMD AM4

Основные операции DRAM

Существует пять основных операций (или четыре, если объединить чтение и запись в одну), которые необходимо выполнить при доступе к данным в DRAM.

Активация открывает одну из строк DRAM в банке и копирует данные из открытой строки в буфер строк.

Восстановление гарантирует, что заряд, который расходуется из каждой ячейки в строке DRAM во время активации, восстанавливается до полного уровня, чтобы предотвратить потерю данных.

Чтение и запись могут выполняться после копирования данных активированной строки в буфер строк.

Precharge освобождает данные из буфера строк, когда контроллер памяти выполняет чтение и запись в активированную строку, и подготавливает банк для активации другой строки.

Из них задержка доступа DRAM в основном состоит из задержки трех операций: активация, восстановление и предварительная зарядка.

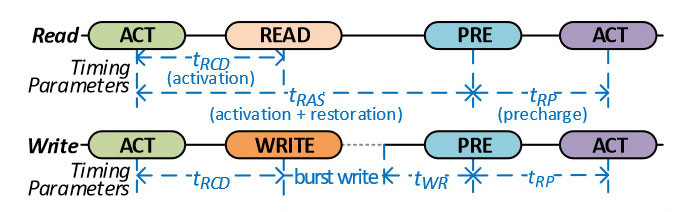

На рисунке выше показана временная шкала команд, выполненных для чтения (вверху) или записи (внизу) для одной строки данных кэша. Контроллер памяти выдает четыре команды: (1) ACT (активировать), (2) READ или (3) WRITE и (4) PRE (предварительная зарядка). Обратите внимание, что восстановление не имеет явной команды, а вместо этого запускается автоматически после команды ACT. Время, затрачиваемое на каждую операцию, определяется набором временных параметров, которые определяются поставщиками DRAM. Хотя каждая команда работает с гранулярностью строк, для простоты мы описываем, как операции DRAM влияют на одну ячейку DRAM.

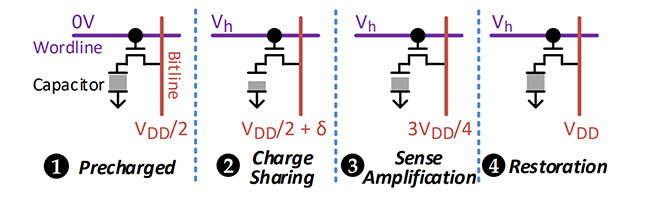

В начальном предварительно заряженном состоянии (1) битовая линия поддерживается на уровне напряжения VDD / 2, где VDD — полное напряжение питания DRAM. Линия слова находится в 0 В, и поэтому битовая линия отключена от конденсатора. После того, как контроллер памяти выдает команду ACT (2), словосочетание повышается до Vh, тем самым соединяя конденсатор ячейки DRAM с разрядной линией. Так как в этом примере напряжение на конденсаторе выше, чем на разрядной линии, заряд поступает на разрядную линию, повышая уровень напряжения до VDD / 2 + δ. Этот процесс называется разделением заряда. Затем усилитель считывания измеряет отклонение на битовой линии и соответственно усиливает это отклонение (3). Эта фаза, называемая чувственным усилением, в конечном итоге приводит уровень напряжения разрядной линии и ячейки к исходному состоянию напряжения ячейки (в данном примере VDD).

Как только усилитель считывания достаточно усилил данные в битовой линии (например, уровень напряжения достигнет 3VDD / 4), контроллер памяти может выдать команду READ или WRITE для доступа к данным ячейки в буфере строк. Время, необходимое для достижения этого состояния (3) после команды ACT, задается параметром синхронизации tRCD, как показано на первом рисунке. После того, как команда READ или WRITE введена, фаза чувствительного усиления продолжает управлять напряжением на битовой линии (4), пока уровень напряжения битовой линии и ячейка не достигнут VDD. Другими словами, исходный уровень заряда ячейки полностью восстанавливается до исходного значения для READ или корректно обновляется до нового значения для WRITE.

Для запросов на чтение DRAM задержка для ячейки, которая будет полностью восстановлена после ACT, определяется параметром синхронизации tRAS. Для запросов записи DRAM время, необходимое для полного обновления ячейки, определяется tWR. После восстановления битовая линия может быть предварительно заряжена с помощью команды PRE, чтобы подготовить подмассив для будущего доступа к другой строке. Этот процесс отключает ячейку от разрядной линии путем понижения напряжения на словарной линии. Затем он сбрасывает напряжение разрядной линии до VDD / 2. Время завершения операции предварительной зарядки определяется параметром синхронизации tRP.

Значения tRCD и tRAS могут быть значительно ниже, чем в даташитах. Как так?

Обычные микросхемы DRAM выполняют операции активации и восстановления с использованием фиксированной задержки, которая определяется значением параметров синхронизации, показанных на первом изображении. Однако существуют способы, с помощью которых задержки для активации и восстановления могут быть уменьшены путем использования текущего уровня заряда ячейки. Если элемент имеет высокий уровень заряда, соответствующий процесс возмущения напряжения на битовой линии во время активации происходит быстрее, и, следовательно, усилителю считывания требуется меньше времени для достижения состояний 3 и 4 на втором изображении. «ChargeCache» — это современный механизм, который использует эту информацию для безопасного уменьшения временных параметров tRCD и tRAS для сильно заряженной ячейки.

ChargeCache отслеживает строки, к которым недавно был получен доступ, что означает, что их ячейки имеют высокий уровень заряда, поскольку с момента последнего восстановления ячеек до полного уровня заряда прошло только короткое время. Поэтому, если недавно активированная строка снова активируется в течение короткого интервала времени (например, 1 мс), ChargeCache использует более низкие значения tRCD и tRAS для строки, что уменьшает общую задержку доступа к DRAM. Аналогичный подход может быть применен для уменьшения времени восстановления. В обычном чипе DRAM каждая команда ACT запускает операцию восстановления, которая полностью восстанавливает уровень заряда ячеек в активированном ряду. Аналогично, каждая операция обновления полностью восстанавливает уровень заряда элемента в фиксированный интервал времени (каждые 64 мс в DDRx DRAM).

Существует также механизм Restore Truncation, который частично восстанавливает уровень заряда ячейки ровно настолько, чтобы сохранять правильные данные — до следующего обновления ячейки. Одним из элементов управления для этого механизма является время tWR и tRAS.

Некоторые предустановки, опубликованные в моей статье, используют эти механизмы, поэтому я советую вам забыть о типичных формулах, которые вы можете найти в Интернете.

Выводы

Поскольку элемент DRAM состоит из конденсатора, элемент теряет заряд, даже когда к нему нет доступа. Чтобы предотвратить потерю данных, DRAM должен выполнять периодические операции обновления для всех ячеек. Операция обновления возвращает уровень заряда ячейки к ее полному значению.

Современные микросхемы памяти позволяют устанавливать агрессивные временные интервалы благодаря механизму Restore Truncation и ChargeCache.

Микросхемы SDRAM в некотором смысле позволяют выполнять третью и четвертую операции параллельно. Если быть точным, команда перезарядки линии PRECHARGE может быть отправлена за определенное количество тактов x до момента, когда был выпущен последний элемент данных запрошенного пакета, не опасаясь возникновения «сломанной» ситуации в переданном пакете (последнее произойдет, если команда PRECHARGE отправит команды READ с периодом времени меньше x).

Чтобы предотвратить потерю данных в ячейках, вы можете увеличить напряжение DRAM или изменить временные характеристики, которые отвечают за предварительную зарядку и обновление. Регулировка tRP и tRFC будет иметь наибольшее влияние, tWR и tRTP также могут помочь. Я не советую поднимать значение tWR выше 12.

tRC> = tRAS + tRP. Для большинства случаев это должна быть оптимальная формула.

tRAS = tRCD + tCL. У меня нет четкого определения для этого тайминга, оно может быть равно tRCD + tCL, но иногда значительно ниже из-за механизмов, перечисленных выше. Также не стоит забывать и о запасе, пределы которого определяются чисто экспериментальным путем, поскольку каждый чип имеет различные характеристики ячеек. Вот вам один из примеров.

Для высоких частот я использую формулу из первого рисунка. tRAS = tRCD + tBL + tWR, где tWR тюнингованное, которое равно 12 или 10. tBL для DDR4 всегда равен 4, но контроллер может использовать и 2.

DDR4 и Ryzen. Нюансы настройки и разгона памяти на платформе AMD AM4

procODT, RTT и CAD_BUS: что это такое и с чем его едят?

Как я упоминал ранее, пользователи столкнулись с огромным количеством проблем, когда вышло первое поколение процессоров Zen. В обзорах была паника, а на форумах было очень мало настоящих экспертов. Единственная тема, которая была — «память плохо разгоняется». Через некоторое время появились первые пресеты от уважаемого Stilt, они стали чудом для сообщества AMD, но, тем не менее, секреты и зависимости не были раскрыты.

Один из самых частых вопросов, который можно найти в форумах о системах Ryzen: «От чего зависит разгон памяти?».

Итак, давайте разбираться. В нашем случае успех разгона зависит от трех компонентов: материнской платы, IMC (контроллера памяти) и самой памяти.

Материнская плата

Большинство плат на базе чипсетов AMD 300 серии имеют T-топологию, и максимальная тактовая частота памяти в большинстве случаев ограничена 3466 МГц. Но есть «фишка», которая позволить нам незначительно подвинуть этот предел. Настройка САПР.

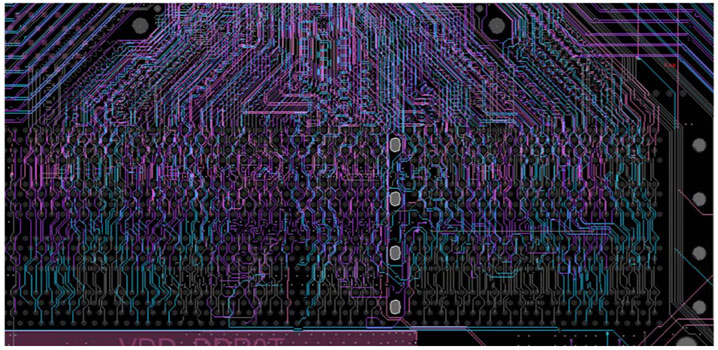

Если нам удастся настроить САПР, то мы сможем получить 3600 МГц. Чтобы понять, почему разгон ограничен такой довольно низкой частотой, нужно взглянуть на печатную плату материнской платы.

Каждая сигнальная трасса на печатной плате является проводником, сигнальной линией, которая может повлиять на другие сигнальные линии. Кроме того, существует вероятность паразитных связей (паразитная индуктивность и высокочастотные помехи). Чтобы бороться с отрицательными связями, каждый разработчик материнской платы должен правильно спроектировать все сигнальные трассы.

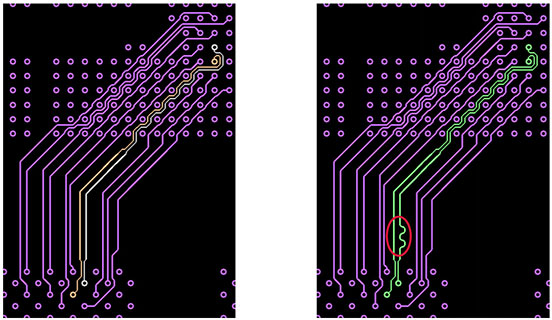

Выше изображено такое изменение конструкции, которое добавляет «кривую», заменяя прямую линию. Это изменение может кардинально изменить возможности сигнальной линии.

Также форм-фактор, количество слоев печатной платы и состав проводников влияют на качество материнской платы. Для плат более дорогого сегмента часто выделяется больше времени на разработку и обычно используются более качественные базовые компоненты. Еще одним ключевым отличием материнских плат на чипсетах серии «X» является увеличенное количество слоев PCB (вместо 3–4 слоев мы имеем 6–8). Это, безусловно, влияет на те самые «паразитные связи». Зачастую на каждой мат плате на одном из краев будет набита надпись, которая свидетельствует о количестве слоев.

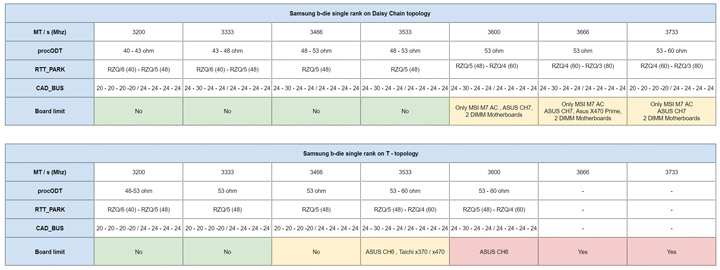

Умные слова это, конечно, интересно, но как распознать качественную материнскую плату? procODT. И чем ниже рабочий procODT, тем лучше результаты разгона, которые вы можете получить на этой материнской плате. Специально для лучшего понимания я создал несколько таблиц, которые могут продемонстрировать вам различия.

В результате мы видим колоссальную разницу между материнскими платами. Я считаю это одной из главных проблем пользователей. И в их выборе, я думаю, виноваты рецензенты материнских плат. За последние два года я не видел обзоров на YouTube, где были рассмотрены топология материнской платы и ее возможности. Рассматривалась коробка, ее содержимое, режимы RGB, как выглядит охлаждение VRM или какая красивая футболку надета на рецензента.

Нет обзоров, в которых вы найдете реальные расчеты возможностей VRM. Вместо этого используются числа, которые существуют только в даташитах при идеальных тестовых условиях и при 25 °C, с идеальным поверхностным монтажом. Одно значение умножается на другие. Вот и весь обзор. Но вернемся к нашей теме.

В качестве бонуса у меня есть еще две рекомендации для вас, на что стоит обратить внимание при покупке материнской платы:

Оперативная память

Я часто слышу на форумах «там есть Samsung B-die, но они работают на низкой частоте и с огромным напряжением, этого не может быть, виновато AMD». Я объясню. Модуль RAM состоит не только из микросхем от конкретного производителя, но и из печатной платы (она тоже имеет определённое количество слоев), на которой мы найдем сотни сигнальных линий. Конденсаторы (обвязка) и, конечно, чип-биннинг оказывают огромное влияние.

Например, мы можем найти в магазинах оперативную память от Corsair — Vengeance RGB Pro 3600MHz C16, которая использует тот самый знаменитый B-die, но мы не найдем рекордов на этом продукте. Рассмотрим другой пример — G.Skill Sniper X F4-3400C16D, который не выглядит «вкусным» по сравнению с предыдущим комплектом от Corsair. Однако, если мы сравним результаты разгона, то получится что-то вроде 3200–3466 МГц с CL14 против 3666–3733 МГц с CL14 в пользу набора G.Skill. Поэтому при выборе оперативной памяти советую посетить форумы.

Нюанс. Так как модуль памяти несет на себе несколько чипов памяти, может возникнуть ситуация, когда один из чипов будет иметь иные вольт-частотные характеристики. Такие чипы могут потребовать на несколько шагов больше напряжения для стабилизации на определенной частоте, чем их братья и сестры. При этом другие микросхемы могут стать нестабильными из-за повышенного напряжения. Идеальным вариантом для пользователя является покупка набора с заводским разгоном более 3600 МГц. Это даст вам дополнительную гарантию того, что все чипы могут достигать целевой частоты (заводской бининг все же штука полезная).

Контроллер памяти

Оба поколения контроллеров памяти Ryzen в большинстве случаев ограничены частотой UCLK 1733–1766 МГц (от DDR-3466 до DDR-3525). Безусловно есть случаи, когда контроллер может работать и на более высоких частотах. Чтобы упростить жизнь нашему контроллеру памяти, можно использовать модули, способные работать с очень низким procODT, что значительно меняет согласование сигналов. Рабочий диапазон procODT, по словам AMD, находится в диапазоне 40–60 Ом. 68 Ом уже за пределами зеленой зоны. Стабильность в этой области будет сильно зависеть от настроек САПР (CAD_BUS) и качества материнской платы.

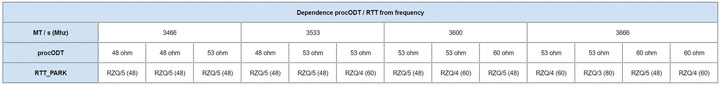

В приведенной выше таблице показано, как procODT / RTT может меняться с ростом частоты DRAM.

Дабы улучшить восприятие этой информации, представьте циферблаты механических часов. procODT будет считать часы, RTT_PARK будет считать минуты, а CAD будет действовать как секундная стрелка. Для каждой частоты циферблаты на часах будут показывать разные результаты. Но есть нюанс, так как AMD очень любит менять настройки контроллера памяти с каждым последующим микрокодом, есть вероятность, что наши «механические часы» сломаются.

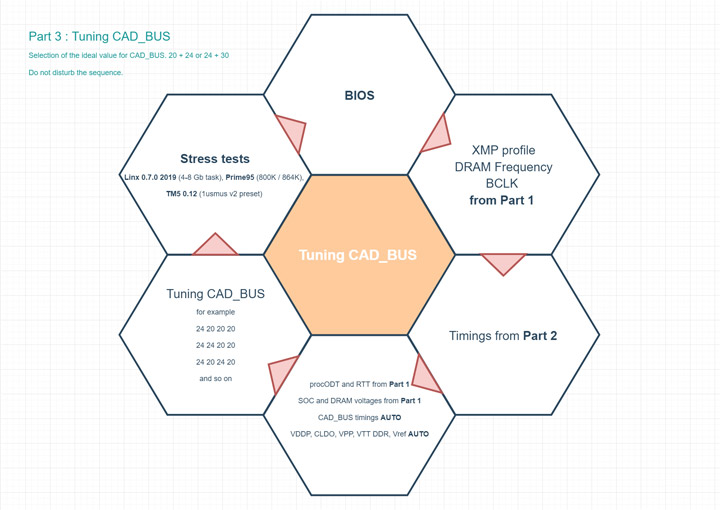

Чтобы быть готовы к подобному повороту событий, мы должны проверить сначала соседние значения RTT_PARK и только затем попытаться изменить procODT. В большинстве случаев кардинальных изменений в прошивках PMU (контроллера памяти) нет. Так же вам не следует спешить менять САПР, поскольку в нем слишком много переменных, и вы можете потерять много времени, пытаясь стабилизировать систему. Существует несколько алгоритмов выбора САПР, но на данный момент я не могу с уверенностью сказать, насколько они эффективны. Я считаю, что САПР не может иметь кардинальных отличий от базовых значений 24-24-24-24, и в большинстве случаев одно из значений можно перемещать вверх или вниз. То есть опция 24-30-24-24 может иметь дополнительный запас безопасности для частоты 3466+ МГц.

Из моих предпочтений это 20-20-20-20, в данном режиме присутствует чуть больший запас «прочности», когда оперативная память подбирается к 52 градусам.

В будущем я постараюсь дополнить эту статью поиском идеального САПР.

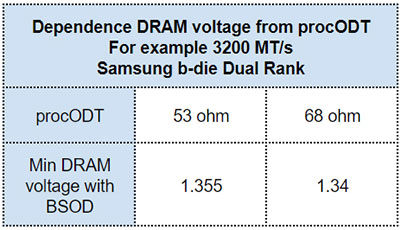

Зависимость рабочего напряжения DRAM от procODT и RTT

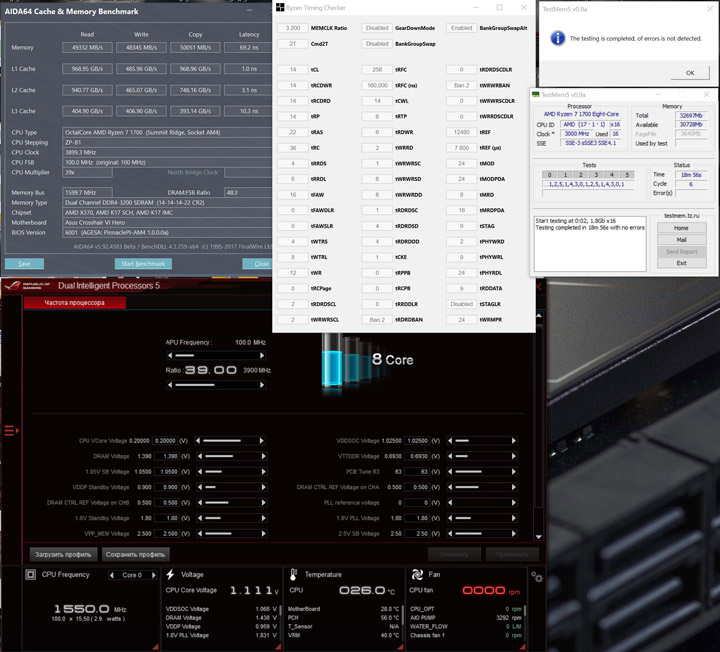

Я провел небольшой тест, в котором использовал разные настройки для напряжения procODT и DRAM. Идея состоит в том, чтобы установить минимально возможное значение DRAM Voltage и избежать BSOD во время теста.

На основании результатов, полученных в этом простом и коротком тесте, мы можем сделать вывод: после изменения procODT стабильное рабочее напряжение DRAM может измениться. Также имеется небольшое влияние RTT на рабочее напряжение памяти.

Холодная загрузка или двойной старт

Нет пользователей процессоров Ryzen, которые не сталкивались с холодным или двойным стартом (иногда даже с тройным). Я могу сразу заверить вас, что в этом нет ничего плохого. Это тесно связано с тренировкой памяти. Когда система не может запуститься в первый раз, запускается алгоритм, который изменяет некоторые параметры, недоступные пользователю, и пытается запустить систему снова. На это явление могут влиять procODT, RTT и CAD.

Иногда внешний BCLK генерируют двойной старт (система тренируется на внутреннем BCLK, а затем на внешнем ). В любом случае, попробуйте следовать рекомендациям калькулятора.

Так же львиная доля успешной тренировки отводится CAD_BUS Timings. Это сложное название является настройкой задержек приемо-передатчика. Формулами я вас томить не буду, конкретные значения будут предлагаться калькулятором, начиная с версии 1.5.2.

DDR4 и Ryzen. Нюансы настройки и разгона памяти на платформе AMD AM4

Терминология

Ниже приведен список технических терминов, относящихся к разгону памяти с процессором Ryzen. Последний использует стандартную архитектуру памяти DDR4, поэтому вы можете быть знакомы с некоторыми из этих терминов. Некоторые другие термины являются новыми и характерными для UEFI материнских плат платформы AM4.

SOC Voltage — напряжение контроллера памяти. Предел 1,2 В.

DRAM Boot Voltage — напряжение, на котором происходит тренировка памяти при запуске системы. Лимит: до 1,45–1,50 В.

VDDP Voltage — это напряжение для транзистора, который конфигурирует содержимое оперативной памяти. Лимит: до 1,1 В.

VPP (VPPM) Voltage — напряжение, которое определяет надежность доступа к строке DRAM.

CLDO_VDDP Voltage — напряжение для DDR4 PHY на SoC. DDR4 PHY, или интерфейс физического уровня DDR4, преобразует информацию, которая поступает из контроллера памяти в формат, понятный модулям памяти DDR4.

Несколько нелогично, что снижение CLDO_VDDP часто может быть более выгодным для стабильности, чем повышение. Опытные оверклокеры также должны знать, что изменение CLDO_VDDP может сдвинуть или устранить дыры в памяти. Небольшие изменения в CLDO_VDDP могут иметь большой эффект, и для CLDO_VDDP нельзя установить значение, превышающее VDIMM –0,1 В. Tсли вы измените это напряжение, то потребуется холодная перезагрузка. Лимит: 1,05 В.

Vref Voltage — источник опорного напряжения оперативной памяти. «Настройка» взаимосвязи контроллера памяти и модуля памяти в зависимости от уровня напряжения, которое рассматривается как «0» или «1»; то есть напряжения, найденные на шине памяти ниже MEMVREF, должны рассматриваться как «0», а напряжения выше этого уровня должны считаться «1». По умолчанию этот уровень напряжения составляет половину VDDIO (около 0,500x). Некоторые материнские платы позволяют пользователю изменять это соотношение, обычно двумя способами: (1) «DRAM Ctrl Ref Voltage» (для линий управления с шины памяти; официальное название JEDEC для этого напряжения — VREFCA) и (2) «DRAM Ctrl Data Ref Voltage» (для строк данных с шины памяти; официальное название JEDEC — VREFDQ). Эти параметры настроены как множитель.

VTT DDR Voltage — напряжение, используемое для управления сопротивлением шины, чтобы достигнуть высокой скорости и поддержать целостность сигнала. Это осуществляется с помощью резистора параллельного прерывания.

PLL Voltage — определяет напряжение питания системы Фазовой АвтоПодстройки Частоты (ФАПЧ или PLL — Phase Locked Loop) и является актуальной лишь для повышения стабильности во время разгона системы с помощью BCLK. Лимит: 1,9 В.

CAD_BUS — САПР командной и адресной шины. Для тех, кто может тренировать память на высоких частотах (>=3466 МГц), но не может стабилизировать ее из-за проблем с сигнализацией. Я предлагаю вам попробовать уменьшить токи привода, связанные с «Командой и адресом» (увеличив сопротивление).

CAD_BUS Timings — задержка трансивера. Значения являются битовой маской (грубой / точной задержки). Аналог RTL/IOL в исполнении AMD. Имеют огромное влияние на тренировку памяти.

procODT — значение сопротивления, в омах, который определяет, как завершенный сигнал памяти терминируется. Более высокие значения могут помочь стабилизировать более высокие скорости передачи данных. Ограничение: нет.

RTT (время приема-передачи) — это время, затраченное на отправку сигнала, плюс время, которое требуется для подтверждения, что сигнал был получен. Это время задержки, следовательно, состоит из времени передачи сигнала между двумя точками. Настройка, которая отвечает за оптимизацию целостности сигнала. DRAM предлагает диапазон значений сопротивления нагрузки. Конкретное сопротивление приемника выводов DQ, представленное интерфейсу, выбирается комбинацией начальной конфигурации микросхемы и рабочей команды DRAM, если включено динамическое завершение на кристалле.

Geardown Mode — позволяет памяти уменьшать эффективную скорость передачи данных на шинах команд и адресов.

Power Down Mode — может незначительно экономить энергию системы за счет более высокой задержки DRAM, переводя DRAM в состояние покоя после периода бездействия.

BankGroupSwap (BGS) — настройка, которая изменяет способ назначения приложениям физических адресов в модулях памяти. Цель этого регулятора — оптимизировать выполнение запросов к памяти, учитывая архитектуру DRAM и тайминги памяти. Теория гласит, что переключение этого параметра может сместить баланс производительности в пользу игр или синтетических приложений.

Игры получают ускорение при отключенной BGS, а пропускная способность памяти AIDA64 была выше при включенной BGS.

Алгоритм настройки системы

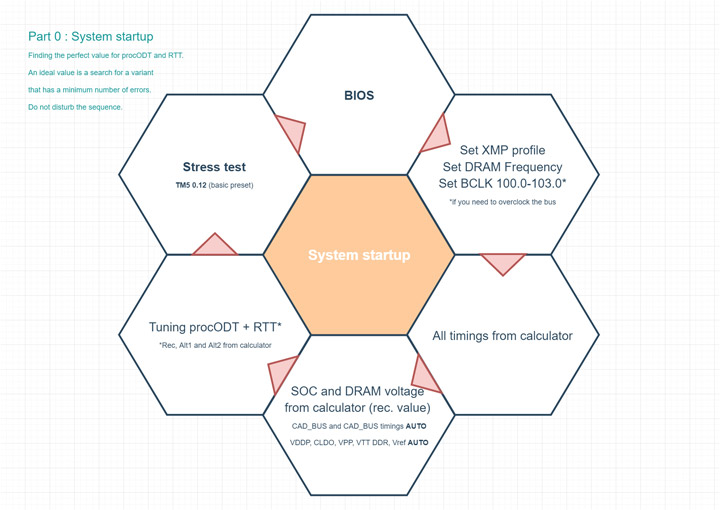

Инструмент, который будет нам помогать с рекомендациями — DRAM Calculator for Ryzen. Самый главный, фундаментальный шаг — это запуск системы на определенной частоте, которую мы хотим получить. Для этого нам потребуется вручную установить такие настройки в UEFI: профиль XMP памяти (он может называться по-разному, смысл от этого не меняется), частоту для оперативной памяти (которую мы хотим получить), установить частоту BCLK (если присутствует такая настройка в прошивке), тайминги (которые рекомендует калькулятор), напряжение для SOC и DRAM (рекомендации калькулятора) и procODT + RTT (NOM, WR и PARK). Не забывайте про важный нюанс, что материнская плата или оперативная память может не справиться с вашими амбициями, потому советую посетить страницу поддержки вашей материнской платы и посмотреть QVL-список, в котором будут указаны частоты, на которых плата в заводских условиях функционировала без ошибок. Эта частота и будет нашей отправной точкой. Зачастую это 3000–3200 МГц.

Параметры procODT + RTT (NOM, WR и PARK) мы будем подбирать так, чтоб система имела минимальное кол-во ошибок. Тестовый пакет TM5 0.12 (Basic Preset). Безусловно, от всех ошибок мы не сможем избавиться, и для этого нам нужен будет следующий шаг.

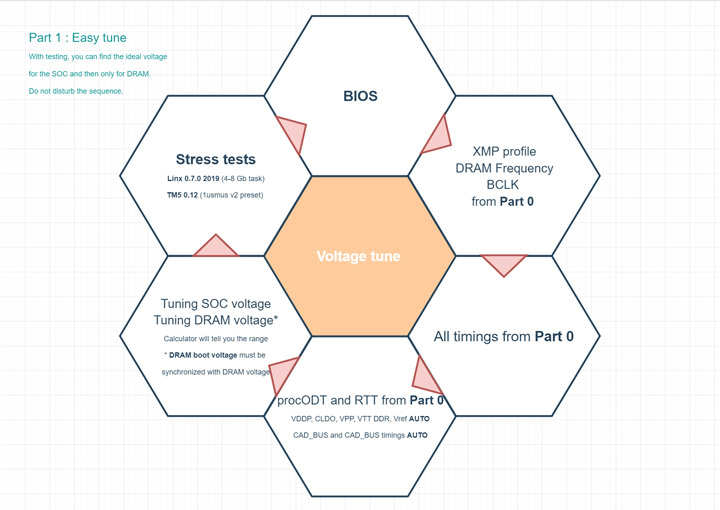

Цель следующего шага — поиск самого оптимального напряжения для DRAM и SOC, при которых система будет иметь минимальное кол-во ошибок. Сначала подбираем напряжение для SOC, а затем для DRAM (калькулятор вам подскажет диапазон). Для отлова ошибок используем тестовый пакет TM5 0.12 (Basic Preset).

В половине случаев вы можете на данном этапе получить полностью стабильную систему. Если тестовый пакет TM5 0.12 не находит ошибок, то вы должны увеличить спектр тестовых программ для проверки стабильности. Вы можете использовать LinX, HCI, Karhu, MEMbench и другие программы. В случае если вышеописанные утилиты нашли ошибку, то вам стоит перейти к следующему шагу, отладочному.

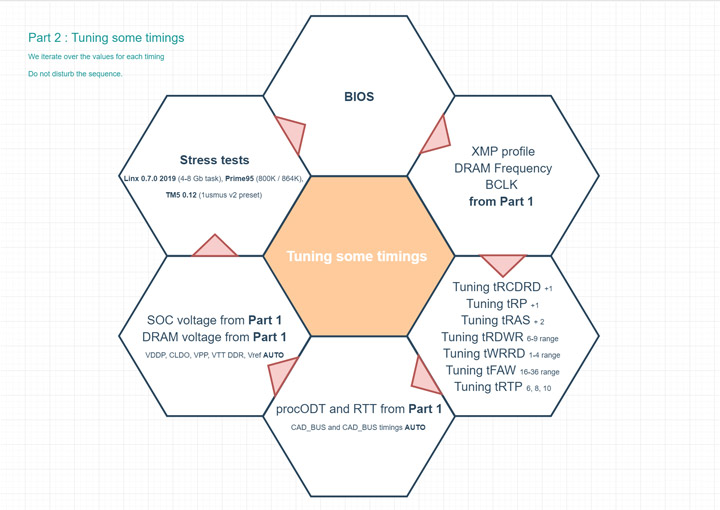

На отладочном шаге главная цель — это изменение определенных таймингов, указанные на иллюстрации ниже.

На данном этапе вы должны проверить по очереди влияние каждого тайминга на стабильность системы. Примечание: я не рекомендую изменять все задержки сразу, постарайтесь набраться терпения. Если тестируемый тайминг никак не улучшает ситуацию, мы его возвращаем на место и проверяем по списку следующую задержку.

На этом шаге основной инструктаж по отладке системы для простых пользователей заканчивается. Дальнейшие шаги я могу посоветовать более опытным оверклокерам, которые знакомы с разгоном достаточно давно.

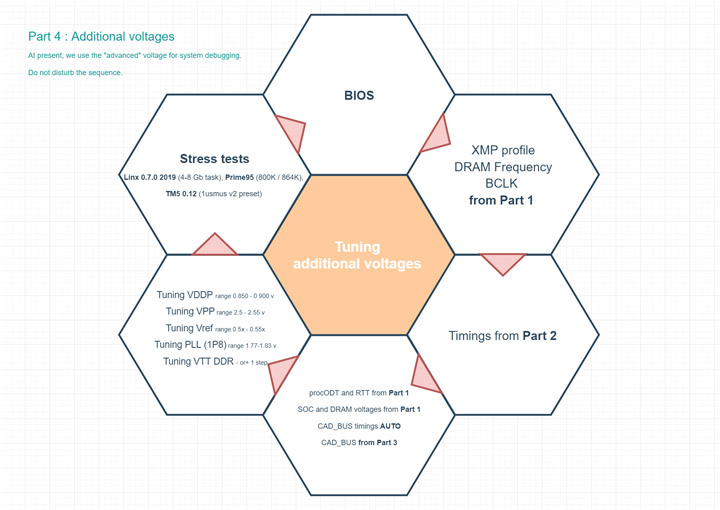

Тонкая настройка CAD_BUS

и корректировка дополнительных напряжений.

На каждой иллюстрации присутствуют списки параметров, которые мы используем или изменяем. Эти списки я сформировал так, чтобы более приоритетные настройки, которые могут помочь улучшить стабильность, вы проверили первыми. Безусловно, вы можете пойти своей дорогой, четких правил и закономерностей нет.